الجا**معةالسعوديةالالكترونية** Saudi Electronic University

**IT 110: Computer Organization**

1

#### **ISA determines instruction formats**

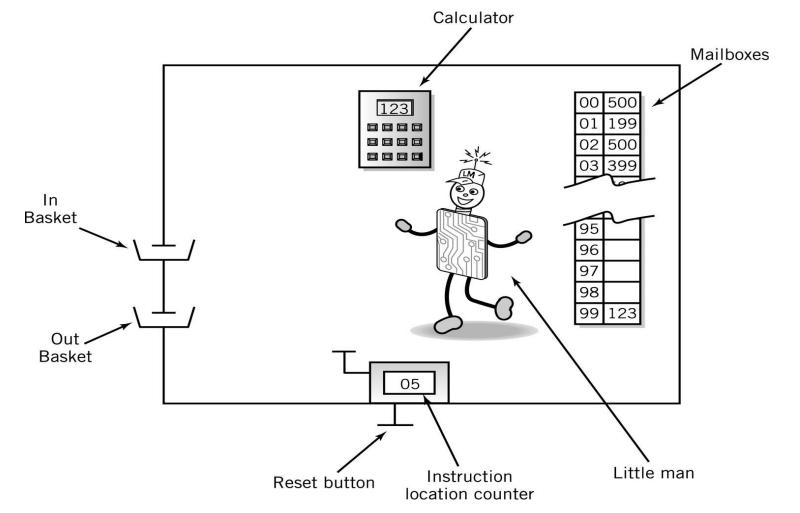

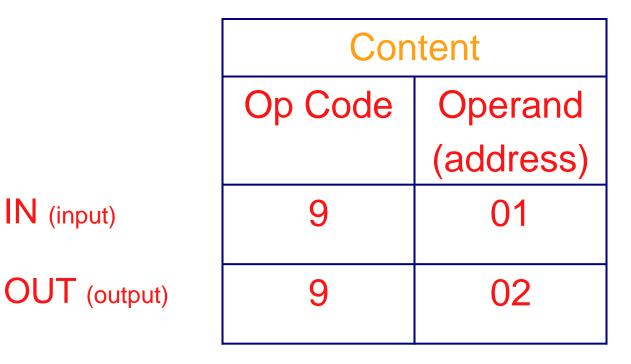

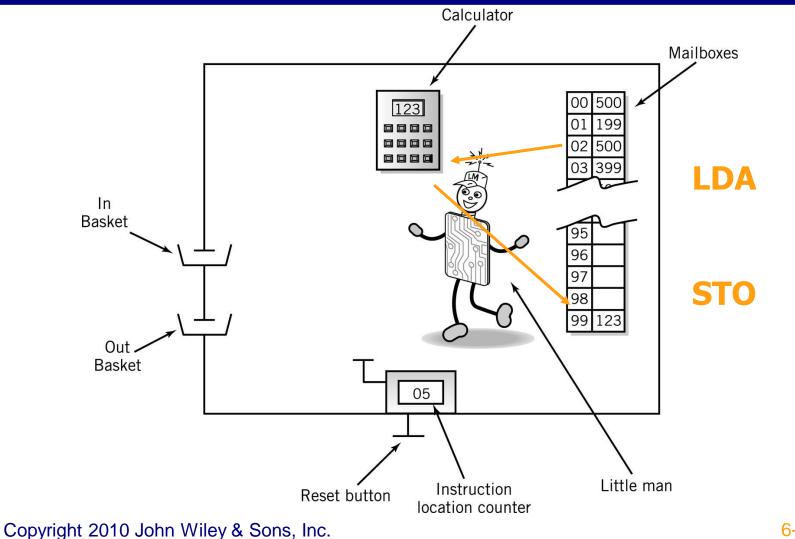

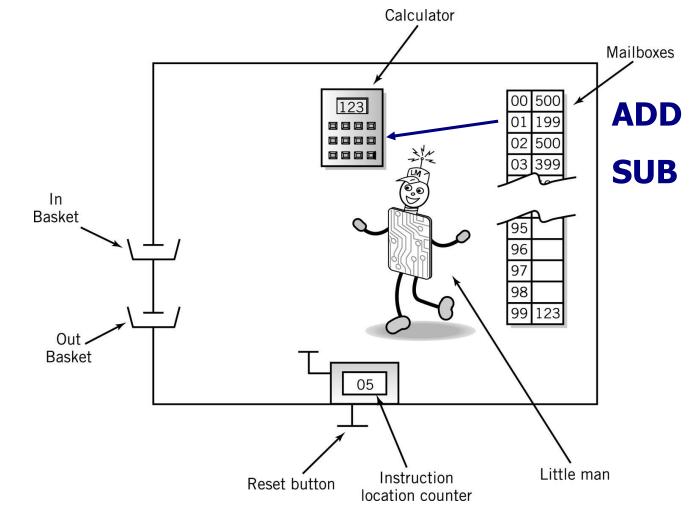

- The LMC is a one-address architecture (an accumulator-based machine).

#### **ISA determines instruction formats**

- The LMC is a one-address architecture (an accumulator-based machine).

- e.g., the instruction ADD X

| Instruction | Mailbox address                      | 1 |

|-------------|--------------------------------------|---|

| _           |                                      |   |

|             | operands. One is                     |   |

| <br>· ·     | cumulator). The<br>dress (location). |   |

#### **ISA determines instruction formats**

- There are other instruction set architectures, all based on the number of explicit operands.

- O-address (stack)

- 1-address (accumulator)

- 2-address

- 3-address

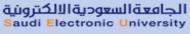

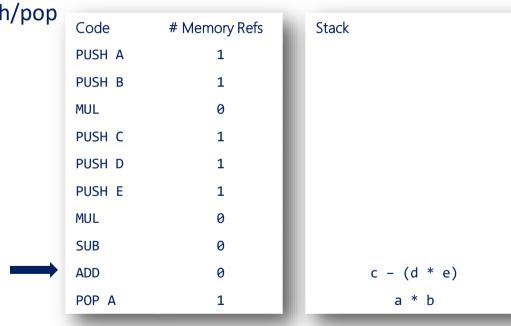

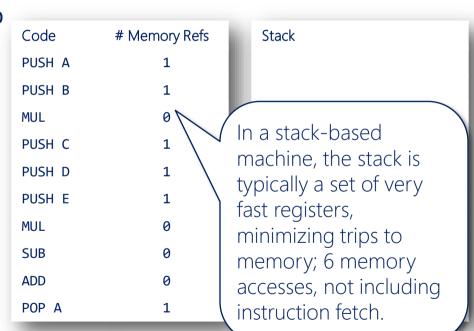

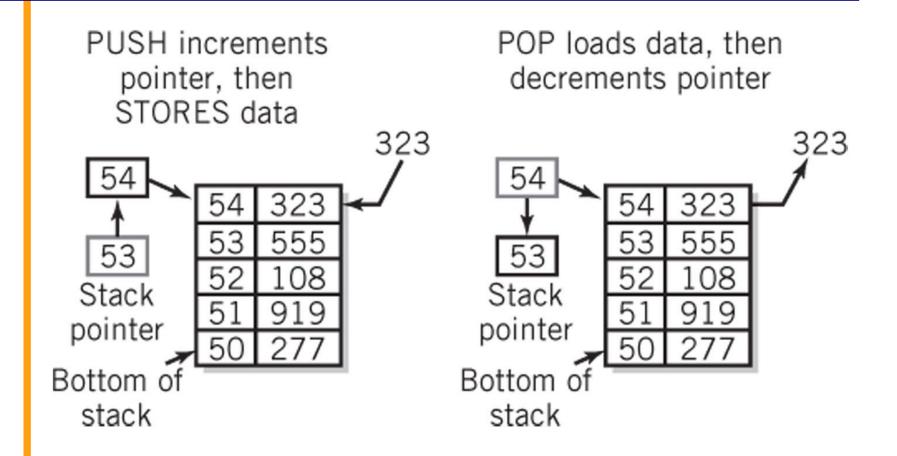

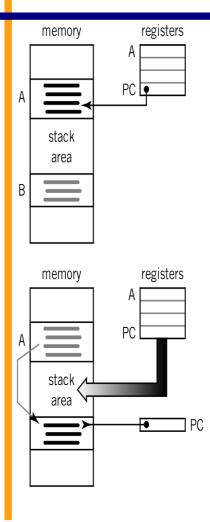

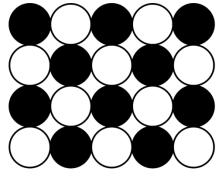

#### **0-Address Machines**

- All operands for binary operations are implicit on the stack. Only push/pop reference memory.

- e.g., calculating a = a \* b + c - d \* e

#### **0-Address Machines**

- All operands for binary operations are implicit on the stack. Only push/pop reference memory.

- e.g., calculating a = a \* b + c - d \* e

| pop   |        |               |       |

|-------|--------|---------------|-------|

| , o p | Code   | # Memory Refs | Stack |

|       | PUSH A | 1             |       |

|       | PUSH B | 1             |       |

|       | MUL    | 0             |       |

|       | PUSH C | 1             |       |

|       | PUSH D | 1             |       |

|       | PUSH E | 1             |       |

|       | MUL    | 0             |       |

|       | SUB    | 0             |       |

|       | ADD    | 0             |       |

|       | POP A  | 1             |       |

|       |        |               |       |

الجامعةالسعوديةالالكترونية Saudi Electronic University

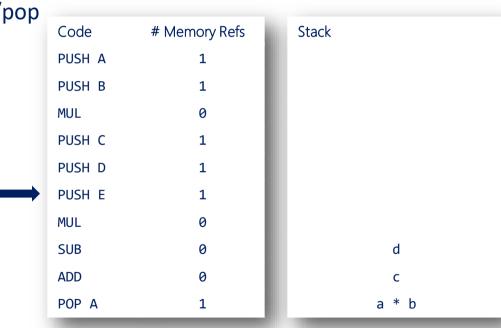

#### **0-Address Machines**

- All operands for binary operations are implicit on the stack. Only push/pop reference memory.

- e.g., calculating a = a \* b + c - d \* e

| 'pop |        |               |       |   |

|------|--------|---------------|-------|---|

| 6.6  | Code   | # Memory Refs | Stack |   |

|      | PUSH A | 1             |       |   |

|      | PUSH B | 1             |       |   |

|      | MUL    | 0             |       |   |

|      | PUSH C | 1             |       |   |

|      | PUSH D | 1             |       |   |

|      | PUSH E | 1             |       |   |

|      | MUL    | 0             |       |   |

|      | SUB    | 0             |       |   |

|      | ADD    | 0             |       |   |

|      | POP A  | 1             |       | а |

|      |        |               |       |   |

الجامعةالسعوديةالالكترونية Saudi Electronic University

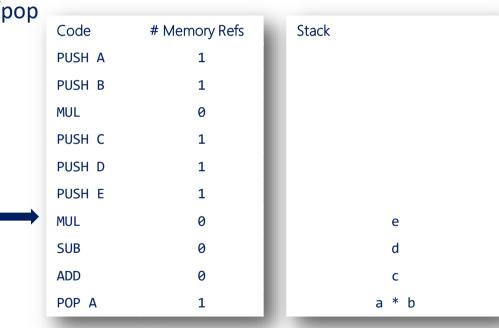

#### **0-Address Machines**

- All operands for binary operations are implicit on the stack. Only push/pop reference memory.

- e.g., calculating a = a \* b + c - d \* e

| 'pop |        |               |       |

|------|--------|---------------|-------|

| · ·  | Code   | # Memory Refs | Stack |

|      | PUSH A | 1             |       |

|      | PUSH B | 1             |       |

|      | MUL    | 0             |       |

|      | PUSH C | 1             |       |

|      | PUSH D | 1             |       |

|      | PUSH E | 1             |       |

|      | MUL    | 0             |       |

|      | SUB    | 0             |       |

|      | ADD    | 0             | b     |

|      | POP A  | 1             | а     |

|      |        |               |       |

الجامعةالسعوديةالالكترونية Saudi Electronic University

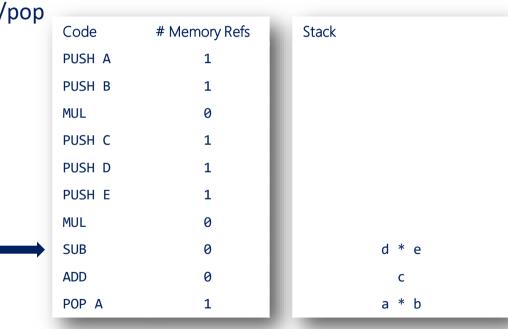

#### **0-Address Machines**

All operands for binary operations are implicit on the stack. Only push/pop reference memory.

- e.g., calculating a = a \* b + c - d \* e

| /pop |        |               |       |

|------|--------|---------------|-------|

| 1 1- | Code   | # Memory Refs | Stack |

|      | PUSH A | 1             |       |

|      | PUSH B | 1             |       |

|      | MUL    | 0             |       |

|      | PUSH C | 1             |       |

|      | PUSH D | 1             |       |

|      | PUSH E | 1             |       |

|      | MUL    | 0             |       |

|      | SUB    | 0             |       |

|      | ADD    | 0             |       |

|      | POP A  | 1             | a * b |

|      |        |               |       |

الجامعةالسعوديةالالكترونية Saudi Electronic University

#### **0-Address Machines**

- All operands for binary operations are implicit on the stack. Only push/pop reference memory.

- e.g., calculating a = a \* b + c - d \* e

| n/pop             |        |               |       |

|-------------------|--------|---------------|-------|

| <i>/ / /</i>      | Code   | # Memory Refs | Stack |

|                   | PUSH A | 1             |       |

|                   | PUSH B | 1             |       |

|                   | MUL    | 0             |       |

|                   | PUSH C | 1             |       |

| $\longrightarrow$ | PUSH D | 1             |       |

|                   | PUSH E | 1             |       |

|                   | MUL    | 0             |       |

|                   | SUB    | 0             |       |

|                   | ADD    | 0             | с     |

|                   | POP A  | 1             | a * b |

|                   |        |               |       |

#### **0-Address Machines**

- All operands for binary operations are implicit on the stack. Only push/pop reference memory.

- e.g., calculating a = a \* b + c - d \* e

الجامعةالسعوديةالالكترونية Saudi Electronic University

#### **0-Address Machines**

- All operands for binary operations are implicit on the stack. Only push/pop reference memory.

- e.g., calculating a = a \* b + c - d \* e

الجامعةالسعوديةالالكترونية Saudi Electronic University

#### **0-Address Machines**

- All operands for binary operations are implicit on the stack. Only push/pop reference memory.

- e.g., calculating

a = a \* b + c d \* e

الجامعةالسعوديةالالكترونية Saudi Electronic University

#### **0-Address Machines**

- All operands for binary operations are implicit on the stack. Only push/pop reference memory.

- e.g., calculating a = a \* b + c - d \* e

الجامعةالسعوديةالالكترونية Saudi Electronic University

#### **0-Address Machines**

- All operands for binary operations are implicit on the stack. Only push/pop reference memory.

- e.g., calculating a = a \* b + c - d \* e

| n/pop          |        |               |                       |

|----------------|--------|---------------|-----------------------|

| <i>·</i> · · · | Code   | # Memory Refs | Stack                 |

|                | PUSH A | 1             |                       |

|                | PUSH B | 1             |                       |

|                | MUL    | 0             |                       |

|                | PUSH C | 1             |                       |

|                | PUSH D | 1             |                       |

|                | PUSH E | 1             |                       |

|                | MUL    | 0             |                       |

|                | SUB    | 0             |                       |

|                | ADD    | 0             |                       |

|                | POP A  | 1             | a * b + (c - (d * e)) |

#### **0-Address Machines**

- All operands for binary operations are implicit on the stack. Only push/pop reference memory.

- e.g., calculating a = a \* b + c - d \* e

| р |        |               |       |

|---|--------|---------------|-------|

| 1 | Code   | # Memory Refs | Stack |

|   | PUSH A | 1             |       |

|   | PUSH B | 1             |       |

|   | MUL    | 0             |       |

|   | PUSH C | 1             |       |

|   | PUSH D | 1             |       |

|   | PUSH E | 1             |       |

|   | MUL    | 0             |       |

|   | SUB    | 0             |       |

|   | ADD    | 0             |       |

|   | POP A  | 1             |       |

|   |        |               |       |

الجامعةالسعوديةالالكترونية Saudi Electronic University

#### **0-Address Machines**

- All operands for binary operations are implicit on the stack. Only push/pop reference memory.

- e.g., calculating

a = a \* b + c d \* e

الجامعةالسعوديةالالكترونية Saudi Electronic University

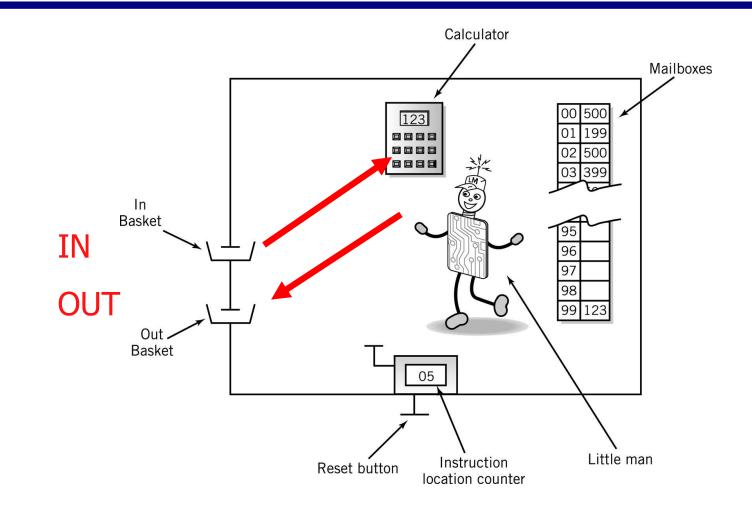

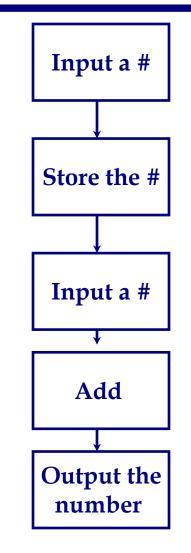

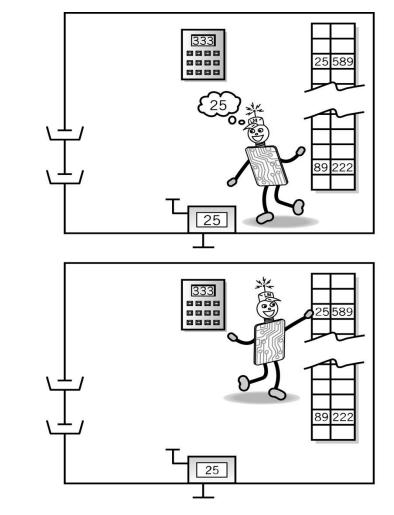

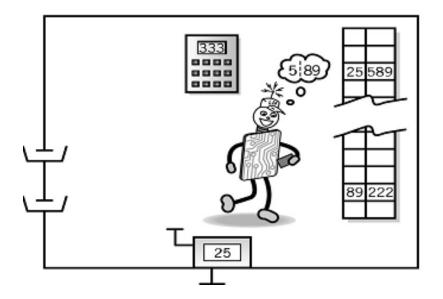

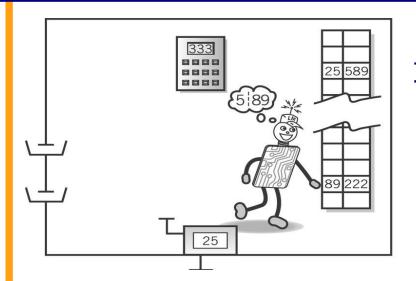

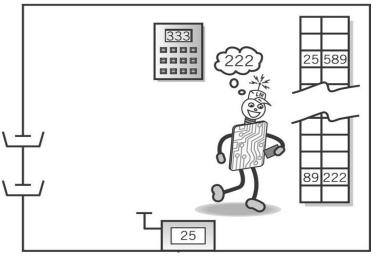

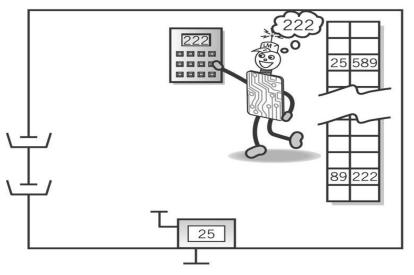

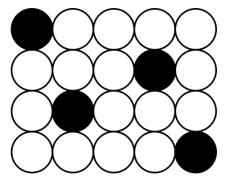

#### **1-Address Machines**

Accumulator is a source and destination. Second source is explicit.

#### **1-Address Machines**

- Accumulator is a source and destination. Second source is explicit.

- e.g., calculating a = a \* b + c - d \* e

| 1<br>1<br>1<br>1 |   |

|------------------|---|

| 1                |   |

| 1                |   |

| _                |   |

| 4                |   |

| 1                |   |

| 1                |   |

| 1                |   |

| 1                |   |

| 1                |   |

| 1                |   |

|                  | 1 |

الجامعةالسعوديةالالكترونية Saudi Electronic University

#### **1-Address Machines**

- Accumulator is a source and destination. Second source is explicit.

- e.g., calculating a = a \* b + c - d \* e

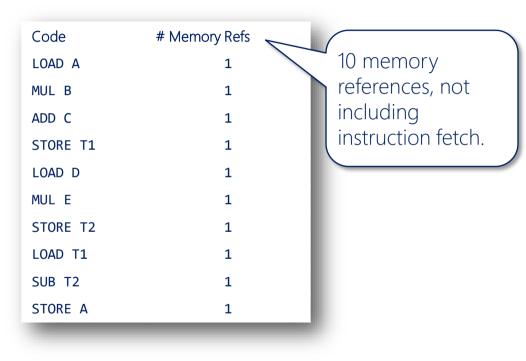

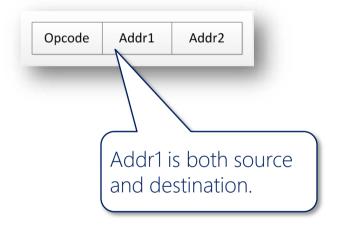

#### **2-Address Machines**

Two source addresses for operands.

One source is also the destination.

الجامعةالسعوديةالالكترونية Saudi Electronic University

#### **2-Address Machines**

- Two source addresses for operands.

One source is also the destination.

- e.g., calculating

a = a \* b + c - d \* e

| # Memory Refs | - 1                             |

|---------------|---------------------------------|

| 2             | - 1                             |

| 3             | - 1                             |

| 3             | - 1                             |

| 2             | - 1                             |

| 3             | - 1                             |

| 3             |                                 |

| 2             | - 1                             |

|               | 2<br>3<br>3<br>2<br>3<br>3<br>3 |

الجامعةالسعوديةالالكترونية Saudi Electronic University

#### **2-Address Machines**

- Two source addresses for operands.

One source is also the destination.

- e.g., calculating

a = a \* b + c - d \* e

| Code       | # Memory Refs | Using memory-to<br>memory |

|------------|---------------|---------------------------|

| MOVE T1, A | 2             | operations, 18            |

| MUL T1, B  | 3             | memory accesses           |

| ADD T1, C  | 3             | (not including            |

| MOVE T2, D | 2             | instruction fetch).       |

| MUL T2, E  | 3             | What if T1 and T2         |

| SUB T1, T2 | 3             | were registers?           |

| MOVE A, T1 | 2             |                           |

الجامعةالسعوديةالالكترونية Saudi Electronic University

#### **2-Address Machines**

- Two source addresses for operands.

One source is also the destination.

- e.g., calculating

a = a \* b + c - d \* e

| Code       | # Memory Refs | Cuts memory<br>references down |

|------------|---------------|--------------------------------|

| MOVE R1, A | 1             | to 6. This is called           |

| MUL R1, B  | 1             | a 1½ address                   |

| ADD R1, C  | 1             | machine with a                 |

| MOVE R2, D | 1             | load/store                     |

| MUL R2, E  | 1             | architecture.                  |

| SUB R1, T2 | 0             |                                |

| MOVE A, R1 | 1             |                                |

الجامعةالسعوديةالالكترونية Saudi Electronic University

#### **3-Address Machines**

One destination operand, two source operands, all explicit

| Opcode | Dst | Src1 | Src2 |

|--------|-----|------|------|

|--------|-----|------|------|

#### **3-Address Machines**

- One destination operand, two source operands, all explicit

- e.g., calculating a = a \* b + c - d \* e

| Code          | # Memory Refs |

|---------------|---------------|

| MPY T1, A, B  | 3             |

| ADD T1, T1, C | 3             |

| MPY T2, D, E  | 3             |

| SUB A, T1, T2 | 3             |

#### **3-Address Machines**

- One destination operand, two source operands, all explicit

- e.g., calculating a = a \* b + c - d \* e

| Code          | # Memory Refs | 12 memory accesses, |

|---------------|---------------|---------------------|

| MPY T1, A, B  | 3             | not including       |

| ADD T1, T1, C | 3             | instruction fetch.  |

| MPY T2, D, E  | 3             | What if T1, T2 were |

| SUB A, T1, T2 | 3             | registers?          |

الجامعةالسعوديةالالكترونية Saudi Electronic University

#### **3-Address Machines**

- One destination operand, two source operands, all explicit

- e.g., calculating a = a \* b + c - d \* e

| Code          | # Memory Refs | 6 memory accesses;     |

|---------------|---------------|------------------------|

| MPY R1, A, B  | 2             | general purpose        |

| ADD R1, R1, C | 1             | registers make a       |

| MPY R2, D, E  | 2             | substantial difference |

| SUB A, R1, R2 | 1             |                        |

الجامعةالسعوديةالالكترونية Saudi Electronic University

#### Comparison

- Assume 8 registers (3 bits),

32 op-codes (5 bits),

15-bit addresses,

16-bit integers.

- Which ISA accesses memory the least?

#### Comparison

- Assume 8 registers (3 bits), 32 op-codes (5 bits), 15-bit addresses, 0-a 16-bit integers.

- Which ISA accesses memory the least?

|                  | Instructions               | Data refs               | Total    |

|------------------|----------------------------|-------------------------|----------|

| 0-address        | 10 x 20 bits = 200<br>bits | 6 x 16 bits = 96 bits   | 296 bits |

| 1-address        | 10 x 20 bits = 200<br>bits | 10 x 16 bits = 160 bits | 360 bits |

| 1½-address       | 7 x 23 bits = 161 bits     | 6 x 16 bits = 96 bits   | 257 bits |

| 2 address        | 7 x 35 bits = 245 bits     | 18 x 16 bits = 288 bits | 519 bits |

| 3-address        | 4 x 50 bits = 200 bits     | 12 x 16 bits =192 bits  | 392 bits |

| 3-address (regs) | 4 x 38 bits = 152 bits     | 6 x 16 bits = 96 bits   | 248 bits |

|                  |                            |                         |          |

الجافعةالسعوديةالالكترونية Saudi Electronic University

#### Comparison

- Assume 8 registers (3 bits 32 op-codes (5 bits), 15-bit addresses, 16-bit integers.

- Which ISA accesses memory the least?

| ts),           | Two clear winners:<br>1½-address (RISC) ar<br>3-address with<br>registers (CISC). | nd                                    | Total    |

|----------------|-----------------------------------------------------------------------------------|---------------------------------------|----------|

| 0-address      | 10 x 20 bits                                                                      | 6 x 16 bits = 96 bits                 | 296 bits |

| 1-address      | 10 x 20 bits = 200<br>bits                                                        | $\sqrt{10 \times 16}$ bits = 160 bits | 360 bits |

| 11/2-address   | 7 x 23 bits = 161 bits                                                            | 6 x 16 bits = 96 bits                 | 257 bits |

| 2 address      | 7 x 35 bits – 245 bits                                                            | 18 x 16 bits – 288 bits               | 519 bits |

| 3-address      | 4 x 50 bits = 200 bits                                                            | 12 x 16 bits =192 bits                | 392 bits |

| 3-address (reg | s) 4 x 38 bits = 152 bits                                                         | 6 x 16 bits = 96 bits                 | 248 bits |

الجامعةالسعوديةالالكترونية Saudi Electronic University

#### Summary

- The instruction set architecture determines the format of instructions (and therefore the assembly language).

- Four basic types with variations:

- O-address (stack)

- 1-address (accumulator)

- 2-address (register variant is 1½-address)

- 3-address (with register variant)

- ISA dramatically affects the number of times memory is accessed.

الجامعةالسعوديةالالكترونية Saudi Electronic University

**IT 110: Computer Organization**

1

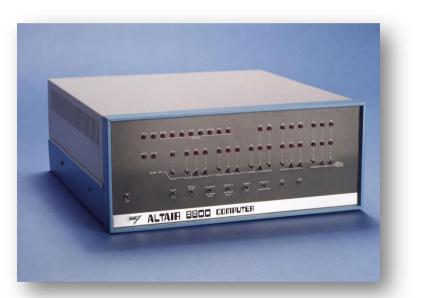

#### **Generations of programming languages**

- First generation: programmed directly in binary using wires or switches.

Image credit: http://professornerdster.com/wp-content/uploads/2012/04/altair\_8800.jpeg

الجامعةالسعوديةالالكترونية Saudi Electronic University

#### **Generations of programming languages**

Second generation: assembly language. Human readable, converted directly to machine code.

Image credit: http://www.coprolite.com/zhb/pooldog/grnscn.jpg

#### **Generations of programming languages**

Third generation: high-level languages, while loops, if-then-else, structured.

Most programming today, including object-oriented.

Image credit: http://www.sunspotworld.com/Tutorial/pngs/swemul06.png

الجامعةالسعوديةالالكترونية Saudi Electronic University

#### IT 110: Computer Organization

4

### **Generations of programming languages**

Fourth generation: 1990s natural languages, non-procedural, report generation. Use programs to generate other programs. Limited use today.

Image credit: http://docs.oracle.com/cd/E13167\_01/aldsp/docs25/appdev/wwimages/CrystalReportsStep4.gif

الجامعةالسعوديةالالكترونية Saudi Electronic University

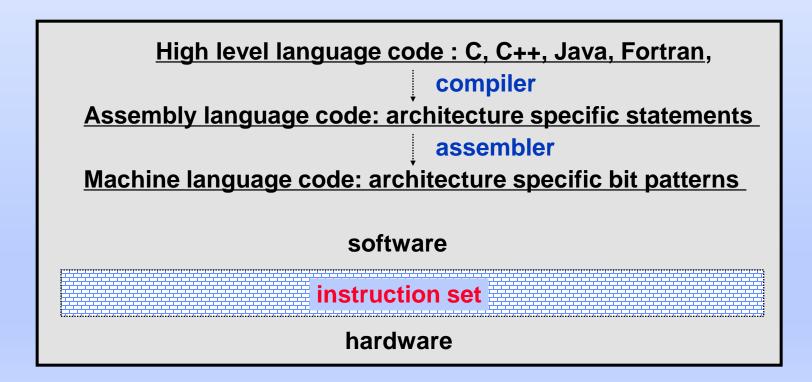

### **Generations of programming languages**

- Key idea: Regardless of the language of writing, computers only process machine code.

- All non-machine code goes through a translation phase into machine code.

- Code generators

- Compilers

- Assemblers

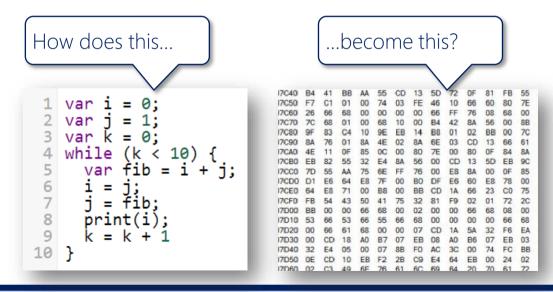

#### Language translation process

- High level languages use comparison constructs, loops, variables, etc.

- Machine code is binary, directly executed by CPU.

الجامعةالسعوديةالالكترونية Saudi Electronic University

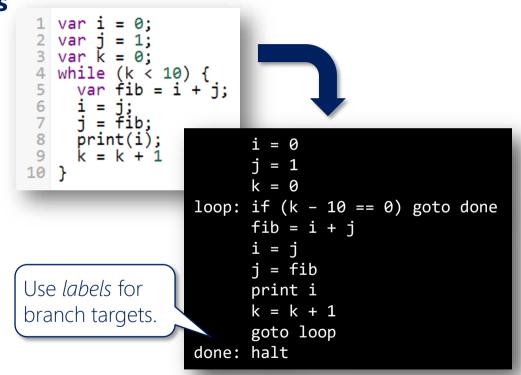

#### Language translation process

Convert high level language to if/goto.

= 0: var п. var = = var 0; while (k < 10) { 5 var fib = i + j; 6 7 8 i = j = fib: print 9 k = 10 }

#### Language translation process

Convert high level language to if/goto.

#### Language translation process

Convert if/goto to assembly (LMC here).

```

loop: LDA k ; if (k - 10 == 0) goto done

SUB

ten ;

BRZ

done ;

i

LDA

; fib = i + j

Þ

ADD

ST0

fib

4

LDA

; i = j

ST0

i

LDA

fib ; j = fib

STO

i

i

LDA

; print i

OUT

;

k

; k = k + 1

LDA

ADD

one

STO

k

BR

loop ; goto loop

done: HLT

; halt

```

#### Language translation process

Convert if/goto to assembly (LMC here).

```

loop: LDA k ; if (k - 10 == 0) goto done

SUB

ten

BRZ

done ;

LDA

; fib = i + j

ADD

i

;

fib

сто

data section

j:

DAT 0

; i = 0

i:

DAT 1 ; j = 1

k:

DAT 0 ; k = 0

fib:

DAT Ø

;

ten:

DAT 10

;

DAT 1

one:

;

ADD

one

•

ST0

k

:

BR

loop ; goto loop

done: HLT

; halt

```

#### Language translation process

- Assemble the instructions to machine code.

| Accomply Langua                  | <b>G</b> O |            |          | Box | Code | Assembler |

|----------------------------------|------------|------------|----------|-----|------|-----------|

| <b>Assembly Langua</b>           | ge         |            |          | 01  | 520  | LDA k     |

|                                  |            |            |          | 02  | 222  | SUB ten   |

| Language translation pro         | ocess      |            |          | 03  | 717  | BRZ done  |

| <ul> <li>Assemble the</li> </ul> | 1          |            | 1.       | 04  | 519  | LDA i     |

| instructions to                  | loop:      | LDA<br>SUB | k<br>ten | 05  | 119  | ADD j     |

| machine code.                    |            | BRZ        | done     | 06  | 321  | STO fib   |

|                                  |            | LDA        | i        | 07  | 519  | LDA j     |

|                                  |            | ADD<br>STO | j<br>fib | 08  | 319  | STO i     |

|                                  |            |            | j        | 09  | 521  | LDA fib   |

|                                  |            | ST0        | i        | 10  | 319  | STO j     |

|                                  |            | LDA<br>STO | fib<br>j | 11  | 519  | LDA i     |

|                                  |            | LDA        | 」<br>i   | 12  | 902  | OUT       |

|                                  |            | OUT        |          | 13  | 520  | LDA k     |

|                                  |            | lda<br>Add | k        | 14  | 123  | ADD one   |

|                                  |            | ST0        | one<br>k | 15  | 320  | STO k     |

|                                  |            | BR         | loop     | 16  | 601  | BR loop   |

|                                  | done:      | HLT        |          | 17  | 000  | HLT       |

الجامعةالسعوديةالالكترونية Saudi Electronic University

| Accomply Lang                         | 1200                                      | Box | Code | Assembler    |

|---------------------------------------|-------------------------------------------|-----|------|--------------|

| Assembly Langu                        | Jage                                      | 01  | 520  | LDA k        |

| Longuogo tropolotion                  |                                           | 02  | 222  | SUB ten      |

| Language translation                  | process                                   | 03  | 717  | BRZ done     |

| <ul> <li>Assemble the</li> </ul>      |                                           |     | 519  | LDA i        |

| instructions to                       | loop: LDA k<br>SUB ten                    | 05  | 119  | ADD j        |

| machine code.                         | BRZ done                                  | 06  | 321  | STO fib      |

|                                       | LDA i                                     | 07  | 519  | LDA j        |

|                                       | ADD j<br>STO fib                          | 08  | 319  | STO i        |

|                                       |                                           | 09  | 521  | LDA fib      |

|                                       | ( j is in box 18                          | 10  | 319  | STO j        |

|                                       | i is in box 19                            |     | 519  | LDA i        |

|                                       | k is in box 20                            | 12  | 902  | OUT          |

|                                       | fib is in box 21                          | 13  | 520  | LDA k        |

|                                       | ten is in box 22                          | 14  | 123  | ADD one      |

|                                       | $\left( \text{ one is in box 23} \right)$ | 15  | 320  | STO k        |

|                                       | BR loop                                   | 16  | 601  | BR loop      |

|                                       | done: HLT                                 | 17  | 000  | HLT          |

| معوديةالالكترونية<br>Saudi Electronic | الجامعةالس<br>University IT               |     |      | Organization |

### Summary

- High level languages are convenient to read and write for humans.

- Computers execute only binary machine code.

- Conversion between the two is required.

- Compilers translate high level languages to machine code.

- Assemblers translate assembly language into machine code.

- Use if/goto pseudo-code as an intermediate language between high level and assembler.

### References

Englander, I. (2009). The architecture of computer hardware and systems software: an information technology approach. Wiley.

# Instruction set architecture ISA

**CISC VS RISC**

### What is an Instruction Set?

- The complete collection of instructions that are understood by a CPU

- Machine Code

- Binary

- Usually represented by assembly codes

## **Instruction Set Architecture (ISA)**

- Serves as an interface between software and hardware.

- Provides a mechanism by which the software tells the hardware what should be done.

### **Elements of an Instruction**

- Operation code (Op code)

- Do this

- Source Operand reference

- To this

- Result Operand reference

- Put the answer here

- Next Instruction Reference

- When you have done that, do this...

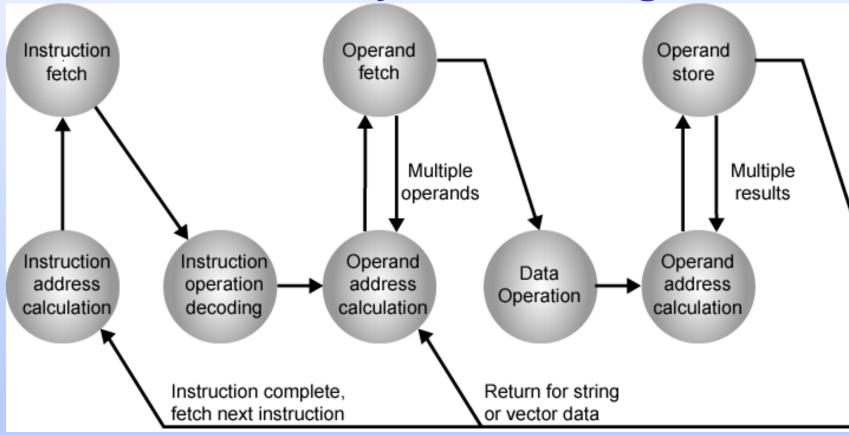

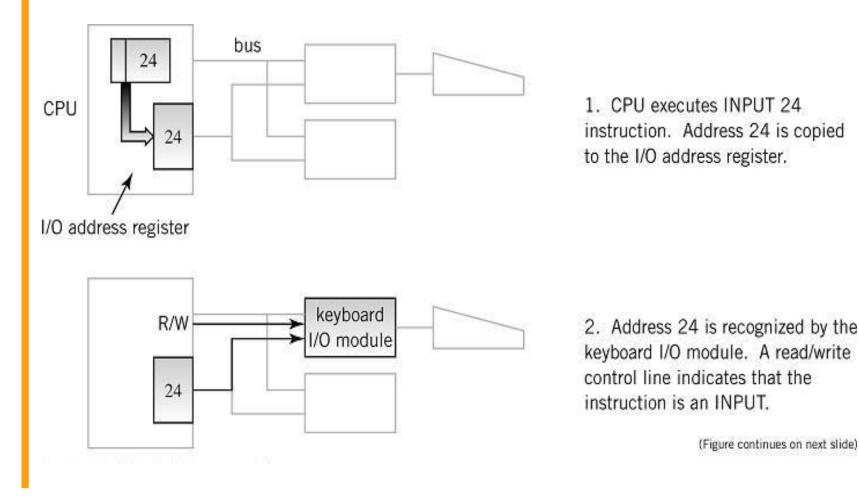

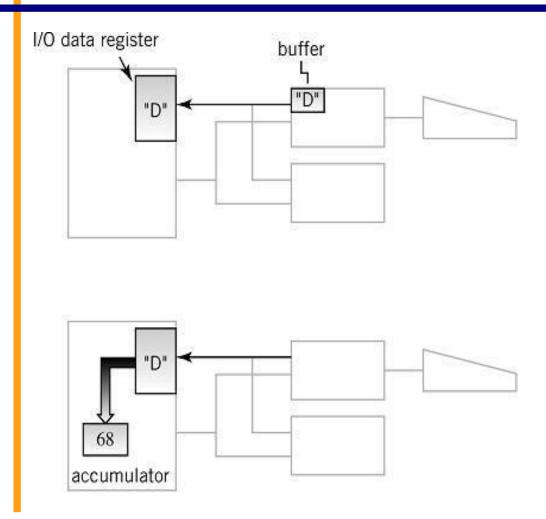

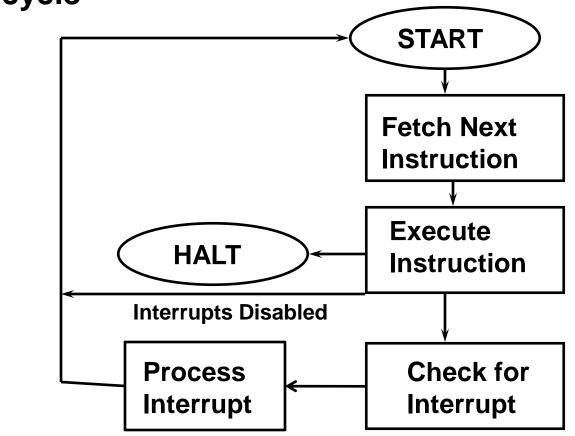

### **Instruction Cycle State Diagram**

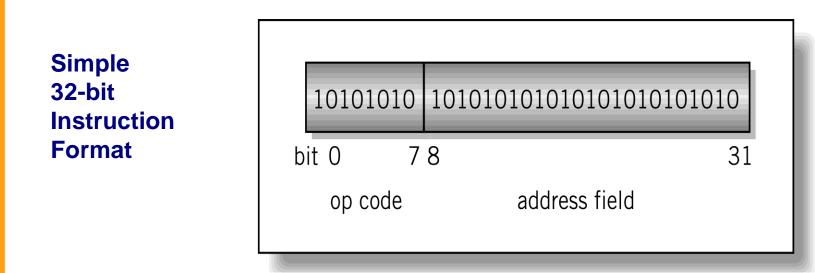

### **Instruction Representation**

- In machine code each instruction has a unique bit pattern

- For human consumption (well, programmers anyway) a symbolic representation is used

- e.g. ADD, SUB, LOAD

- Operands can also be represented in this way

- ADD A,B

### **Simple Instruction Format**

| 4 bits | 6 bits            | 6 bits            |

|--------|-------------------|-------------------|

| Opcode | Operand Reference | Operand Reference |

| ≺      | 16 bits           |                   |

### **Instruction Types**

- Data processing

- Data storage (main memory)

- Data movement (I/O)

- Program flow control

### Number of Addresses (a)

3 addresses

### a=(a\*b+c)-d\*e

- Operand 1, Operand 2, Result

- − a = b + c;

- May be a forth next instruction (usually implicit)

- Not common

- Needs very long words to hold everything

| Code          | # Memory Refs |

|---------------|---------------|

| MPY T1, A, B  | 3             |

| ADD T1, T1, C | 3             |

| MPY T2, D, E  | 3             |

| SUB A, T1, T2 | 3             |

### Number of Addresses (b)

2 addresses

### a=(a\*b+c)-d\*e

- One address doubles as operand and result

- a = a + b

- Reduces length of instruction

- Requires some extra work

- » Temporary storage to hold some results

| Code       | # Memory Refs |

|------------|---------------|

| MOVE T1, A | 2             |

| MUL T1, B  | 3             |

| ADD T1, C  | 3             |

| MOVE T2, D | 2             |

| MUL T2, E  | 3             |

| SUB T1, T2 | 3             |

| MOVE A, T1 | 2             |

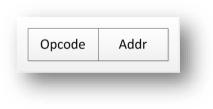

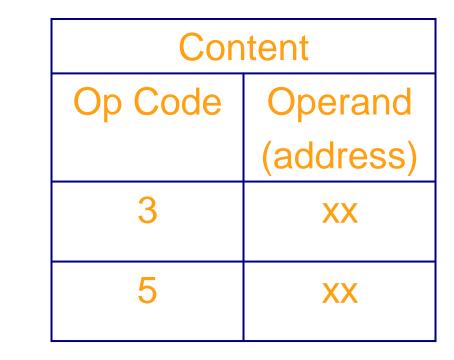

### Number of Addresses (c)

### 1 address

- Implicit second address

- Usually a register (accumulator)

- Common on early machines

### a=(a\*b+c)-d\*e

| Code     | # Memory Refs |

|----------|---------------|

| LOAD A   | 1             |

| MUL 8    | 1             |

| ADD_C    | 1             |

| STORE T1 | 1             |

| LOAD D   | 1             |

| MUL E    | 1             |

| STORE T2 | 1             |

| LOAD T1  | 1             |

| SUB T2   | 1             |

| STORE A  | 1             |

### Number of Addresses (d)

### • 0 (zero) addresses

- All addresses implicit

- Uses a stack

- e.g. push a

- push b

- add

- pop c

### a=a\*b+(c-(d\*e))

| Code   | # Memory<br>Refs |  |

|--------|------------------|--|

| PUSH A | 1                |  |

| PUSH B | 1                |  |

| MUL    | 0                |  |

| PUSH C | 1                |  |

| PUSH D | 1                |  |

| PUSH E | 1                |  |

| MUL    | 0                |  |

| SUB    | 0                |  |

| ADD    | 0                |  |

| POP A  | 1                |  |

### **How Many Addresses**

### More addresses

- More complex (powerful?) instructions

- More registers

- » Inter-register operations are quicker

- Fewer instructions per program

### Fewer addresses

- Less complex (powerful?) instructions

- More instructions per program

- Faster fetch/execution of instructions

# **Design Decisions (1)**

### Operation repertoire

- How many ops?

- What can they do?

- How complex are they?

- Data types

- Instruction formats

- Length of op code field

- Number of addresses

# **Design Decisions (2)**

- Registers

- Number of CPU registers available

- Which operations can be performed on which registers?

- Addressing modes

- RISC v CISC

## **History of RISC/CISC**

- 1950s IBM instituted a research program

- 1964 Release of System/360

- Mid-1970s improved measurement tools demonstrated on CISC

- 1975 801 project initiated at IBM's Watson Research Center

- 1979 32-bit RISC microprocessor (801) developed led by Joel Birnbaum

- 1984 MIPS developed at Stanford, as well as projects done at Berkeley

- 1988 RISC processors had taken over high-end of the workstation market

- Early 1990s IBM's POWER (*Performance Optimization With Enhanced RISC*) architecture introduced w/ the RISC System/6k

- AIM (Apple, IBM, Motorola) alliance formed, resulting in PowerPC

### What is CISC?

- CISC is an acronym for Complex Instruction Set Computer and are chips that are easy to program and which make efficient use of memory. Since the earliest machines were programmed in assembly language and memory was slow and expensive, the CISC philosophy made sense, and was commonly implemented in such large computers as the PDP-11 and the DECsystem 10 and 20 machines.

- Most common microprocessor designs such as the Intel 80x86 and Motorola 68K series followed the CISC philosophy.

- But recent changes in software and hardware technology have forced a reexamination of CISC and many modern CISC processors are hybrids, implementing many RISC principles.

- CISC was developed to make compiler development simpler. It shifts most of the burden of generating machine instructions to the processor. For example, instead of having to make a compiler write long machine instructions to calculate a squareroot, a CISC processor would have a built-in ability to do this.

### **CISC** Attributes

The design constraints that led to the development of CISC (small amounts of slow memory and fact that most early machines were programmed in assembly language) give CISC instructions sets some common characteristics:

- A 2-operand format, where instructions have a source and a destination. Register to register, register to memory, and memory to register commands. Multiple addressing modes for memory, including specialized modes for indexing through arrays

- Variable length instructions where the length often varies according to the addressing mode

- Instructions which require multiple clock cycles to execute.

E.g. Pentium is considered a modern CISC processor

Most CISC hardware architectures have several characteristics in common:

- Complex instruction-decoding logic, driven by the need for a single instruction to support multiple addressing modes.

- A small number of *general purpose registers*. This is the direct result of having instructions which can operate directly on memory and the limited amount of chip space not dedicated to instruction decoding, execution, and microcode storage.

- Several special purpose registers. Many CTSC designs set aside special registers for the stack pointer, interrupt handling, and so on. This can simplify the hardware design somewhat, at the expense of making the instruction set more complex.

- A 'Condition code" register which is set as a side-effect of most instructions. This register reflects whether the result of the last operation is less than, equal to, or greater than zero and records if certain error conditions occur.

At the time of their initial development, CISC machines used available technologies to optimize computer performance.

- Microprogramniing is as easy as assembly language to implement, and much less expensive than hardwiring a control unit.

- The ease of microcoding new instructions allowed designers to make CISC machines upwardly compatible: a new computer could run the same programs as earlier computers because the new computer would contain a superset of the instructions of the earlier computers.

- As each instruction became more capable, fewer instructions could be used to implement a given task. This made more efficient use of the relatively slow main memory.

- Because microprogram instruction sets can be written to match the constructs of high-level languages, the compiler does not have to be as complicated.

### **CISC** Disadvantages

Designers soon realised that the CISC philosophy had its own problems, including:

- Earlier generations of a processor family generally were contained as a subset in every new version - so instruction set & chip hardware become more complex with each generation of computers.

- So that as many instructions as possible could be stored in memory with the least possible wasted space, individual instructions could be of almost any length - this means that different instructions will take different amounts of clock time to execute, slowing down the overall performance of the machine.

- Many specialized instructions aren't used frequently enough to justify their existence -approximately 20% of the available instructions are used in a typical program.

- CISC instructions typically set the condition codes as a side effect of the instruction. Not only does setting the condition codes take time, but programmers have to remember to examine the condition code bits before a subsequent instruction changes them.

### What is **RISC**?

#### • RISC?

RISC, or *Reduced Instruction Set Computer*. is a type of microprocessor architecture that utilizes a small, highly-optimized set of instructions, rather than a more specialized set of instructions often found in other types of architectures.

#### • History

The first RISC projects came from IBM, Stanford, and UC-Berkeley in the late 70s and early 80s. The IBM 801, Stanford MIPS, and Berkeley RISC 1 and 2 were all designed with a similar philosophy which has become known as RISC. Certain design features have been characteristic of most RISC processors:

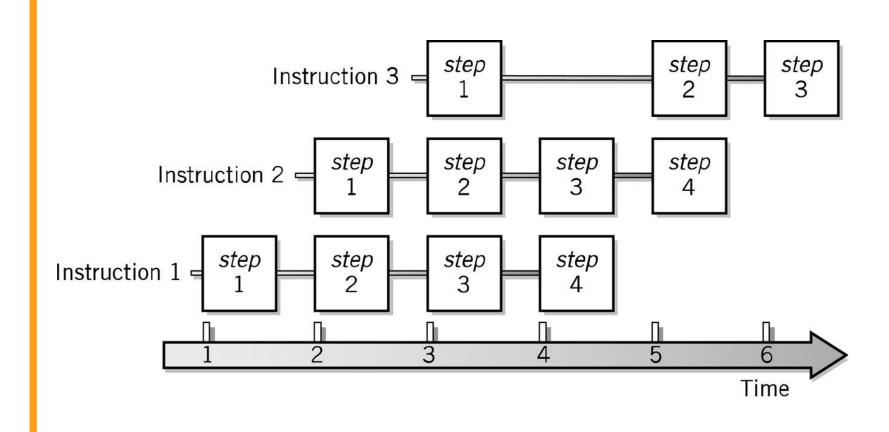

- one cycle execution time: RISC processors have a CPI (clock per instruction) of one cycle. This is due to the optimization of each instruction on the CPU and a technique called PIPELINING

- pipelining: a techique that allows for simultaneous execution of parts, or stages, of instructions to more efficiently process instructions;

- large number of registers: the RISC design philosophy generally incorporates a larger number of registers to prevent in large amounts of interactions with memory

### **RISC Attributes**

The main characteristics of CISC microprocessors are:

- Extensive instructions.

- Complex and efficient machine instructions.

- Microencoding of the machine instructions.

- Extensive addressing capabilities for memory operations.

- Relatively few registers.

In comparison, RISC processors are more or less the opposite of the above:

- Reduced instruction set.

- Less complex, simple instructions.

- Hardwired control unit and machine instructions.

- Few addressing schemes for memory operands with only two basic instructions, LOAD and

- STORE

- Many symmetric registers which are organised into a register file.

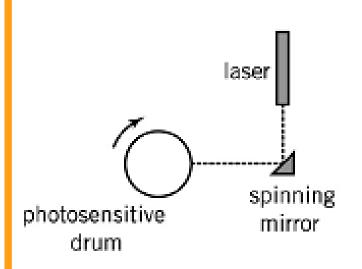

# **Pipelining**

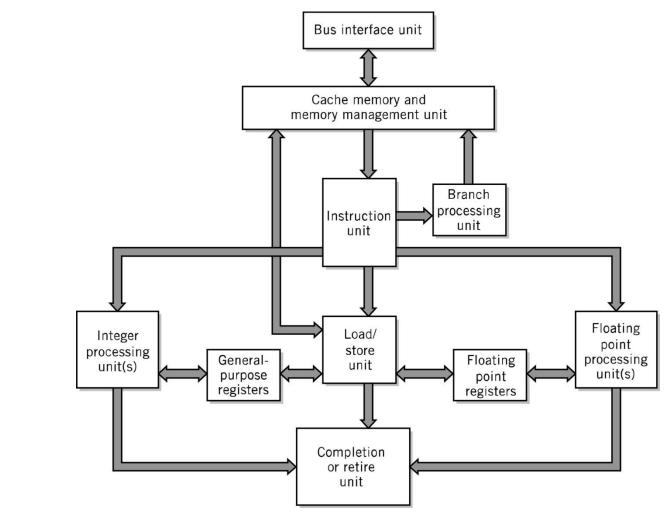

#### **RISC Pipelines**

A RISC processor pipeline operates in much the same way, although the stages in the pipeline are different. While different processors have different numbers of steps, they are basically variations of these five, used in the MIPS R3000 processor:

- fetch instructions from memory

- read registers and decode the instruction

- execute the instruction or calculate an address

- access an operand in data memory

- write the result into a register

#### **RISC Disadvantages**

- There is still considerable controversy among experts about the ultimate value of RISC architectures. Its proponents argue that RISC machines are both cheaper and faster, and are therefore the machines of the future.

- However, by making the hardware simpler, RISC architectures put a greater burden on the software. Is this worth the trouble because conventional microprocessors are becoming increasingly fast and cheap anyway?

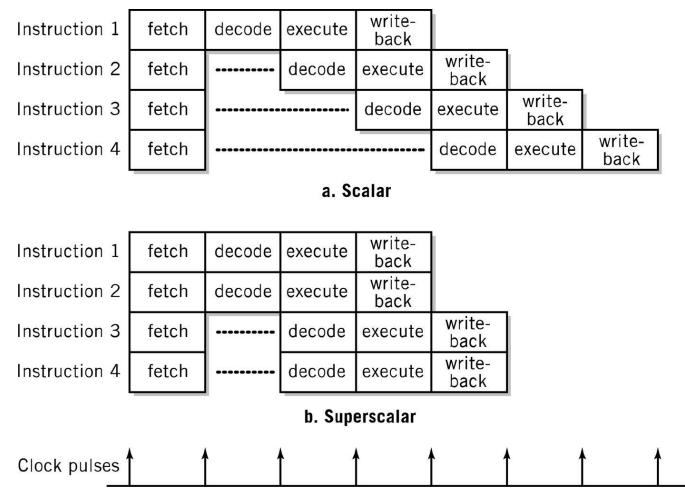

#### **CISC versus RISC**

#### CISC

Emphasis on hardware

Includes multi-clock complex instructions

Memory-to-memory: "LOAD" and "STORE" incorporated in instructions

Small code sizes, high cycles per second

Transistors used for storing complex instructions

#### RISC

Emphasis on software

Single-clock, reduced instruction only

Register to register: "LOAD" and "STORE" are independent instructions

Low cycles per second, large code sizes

Spends more transistors on memory registers

### **Summation**

- As memory speed increased, and high-level languages displaced assembly language, the major reasons for CISC began to disappear, and computer designers began to look at ways computer performance could be optimized beyond just making faster hardware.

- One of their key realizations was that a sequence of simple instructions produces the same results as a sequence of complex instructions, but can be implemented with a simpler (and faster) hardware design. (Assuming that memory can keep up.) RISC (Reduced Instruction Set Computers) processors were the result.

- CISC and RISC implementations are becoming more and more alike. Many of today's RISC chips support as many instructions as yesterday's CISC chips. And today's CISC chips use many techniques formerly associated with RISC chips.

- To some extent, the argument is becoming moot because CISC and RISC implementations are becoming more and more alike. Many of today's RISC chips support as many instructions as yesterday's CISC chips. And today's CISC chips use many techniques formerly associated with RISC chips.

### CHAPTER 1: Computers and Systems

### The Architecture of Computer Hardware, Systems Software & Networking: An Information Technology Approach 4th Edition, Irv Englander John Wiley and Sons ©2010

PowerPoint slides authored by Wilson Wong, Bentley University PowerPoint slides for the 3<sup>rd</sup> edition were co-authored with Lynne Senne, Bentley University

### **Typical Computer Ad**

#### **TECHNOLOGY CHOICES TO BUILD YOUR BUSINESS**

#### **New! Vostre 400 Mini Tower**

Only Drex delivers this combination of performance and expandibility in a system designed exclusively for Small Businessesthe Vostre 400.

DREX

- Intex Core 2 Duo Processor

- Genuine Home Basic Operating System

- 2GB DDR2 SDRAM

- 160GB SATA Hard Drive

- 16x DVD+/-RW Drive

- 256MB PCI Express Graphics Card

- 1-Yr Limited Warranty, Next Business Day On-Site Service, and Hardware Warranty Support

- 20" Widescreen Flat Panel Display

NEW! Lower-priced upgrades: Upgrade to 4GB Memory, 250GB Hard Drive, only \$90!!

- Is the computer fast enough to run necessary programs?

- Is the computer cost-effective?

- Will it be obsolete in 6 months?

### Why Study Computer System Architecture?

- User

- Understand system capabilities and limitations

- Make informed decisions

- Improve communications with information technology professionals

- Programmer

- Create efficient application software for specific processing needs

- Systems Architect or Systems Analyst

- Specify computer systems and architecture to meet application requirements

- Make intelligent decisions about system strategy

# the second

### Why Study Computer System Architecture?

- System Administrator / Manager

- Install, configure, maintain, and upgrade computer systems

- Maximize system availability and efficiency

- Optimize system performance

- Ensure system security

- Web Services Designer

- Optimize customer accessibility to Web services

- Optimize web system configurations

- Select appropriate data formats, page designs and scripting languages

- Design efficient Web pages

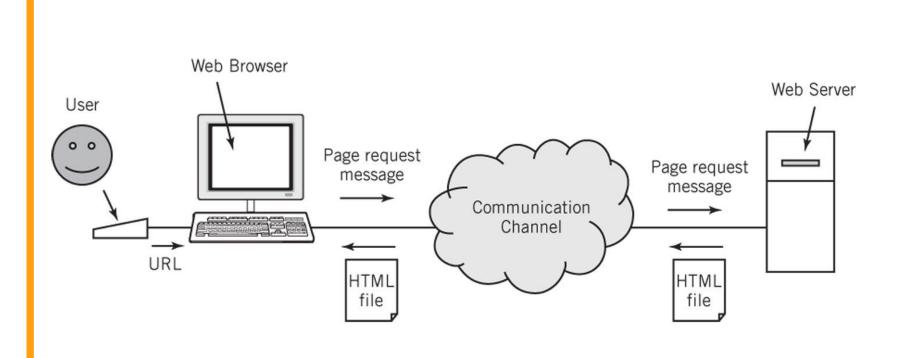

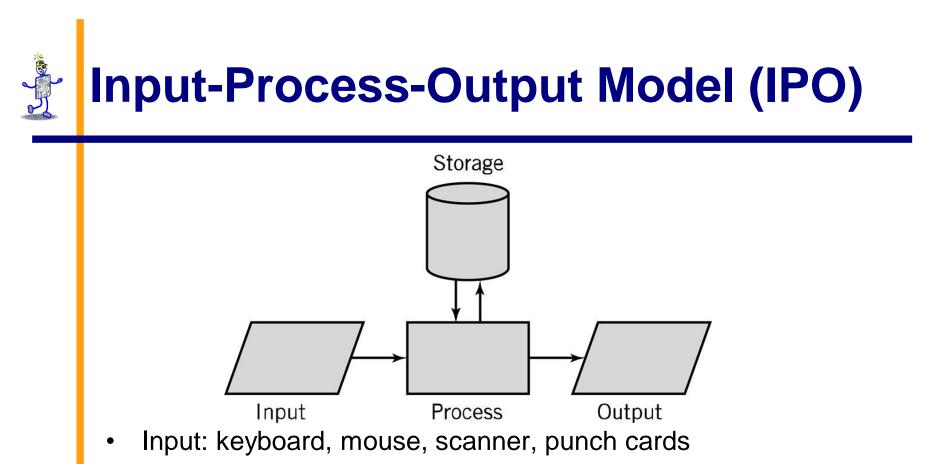

## Web Browser Application Use

- Processing: CPU executes the computer program

- Output: monitor, printer, fax machine

- Storage: hard drive, optical media, diskettes, magnetic tape

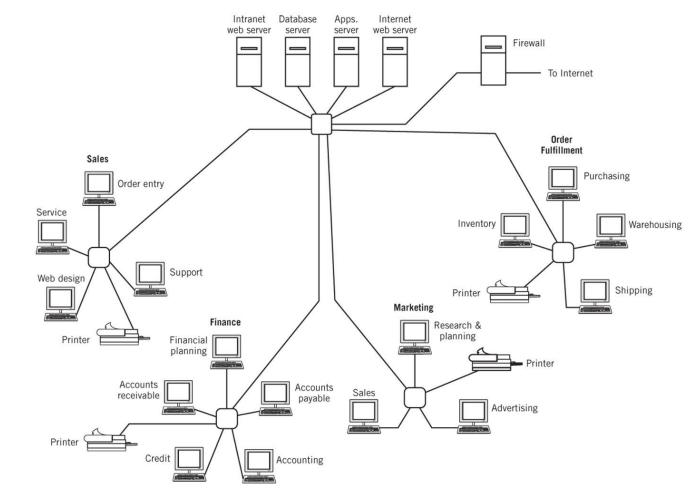

### Simplified IT Computer System Layout

### **Computer System Components**

- Hardware

- Processes data by executing instructions

- Provides input and output

- Control input, output and storage components

- Software

- Applications and system software

- Instructions tell hardware exactly what tasks to perform and in what order

- Data

- Fundamental representation of facts and observations

- Communications

- Sharing data and processing among different systems

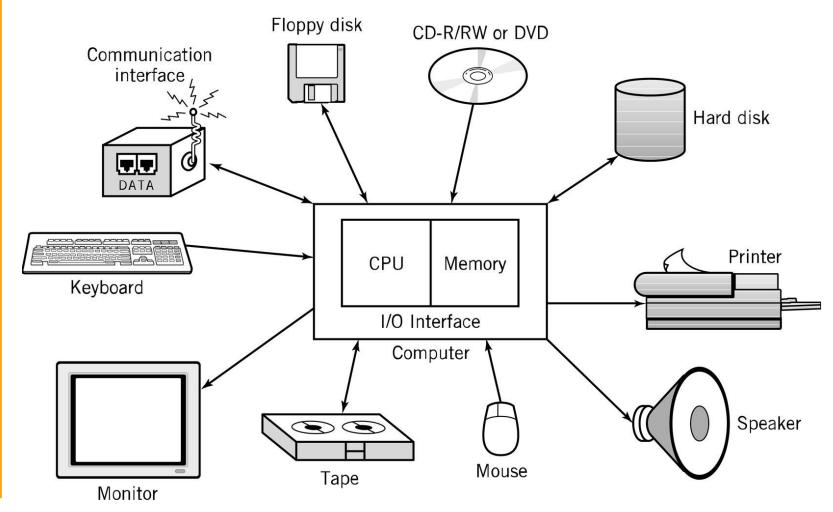

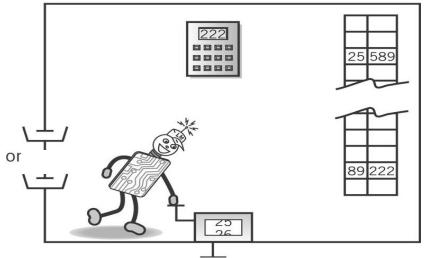

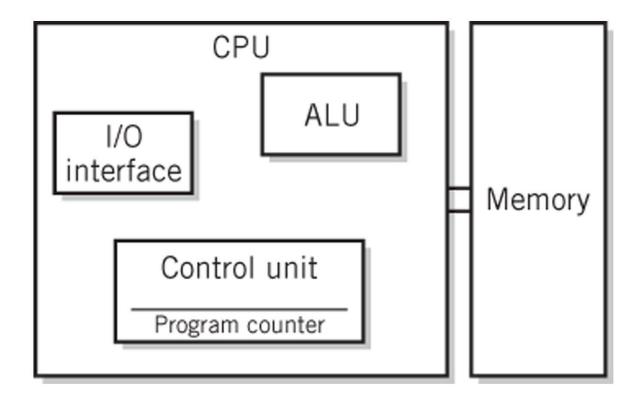

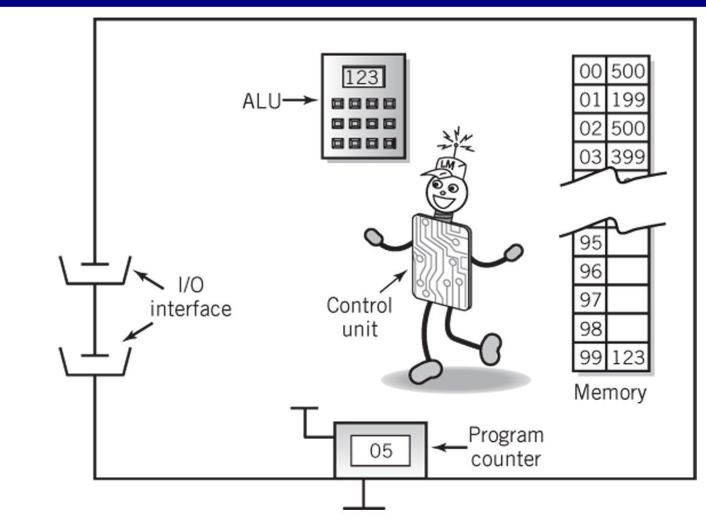

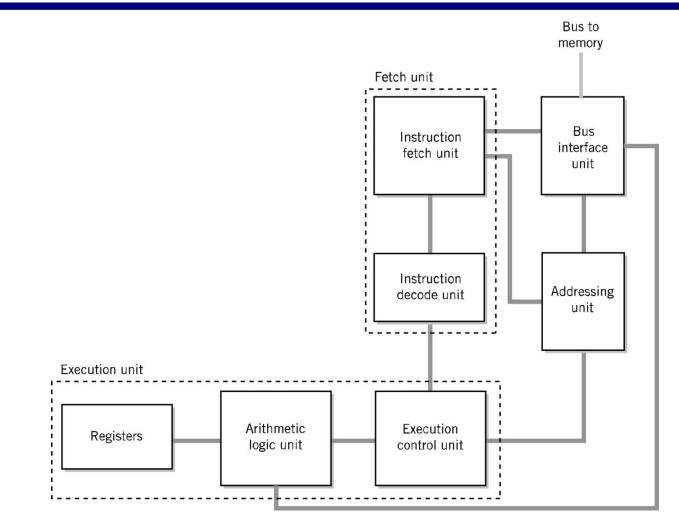

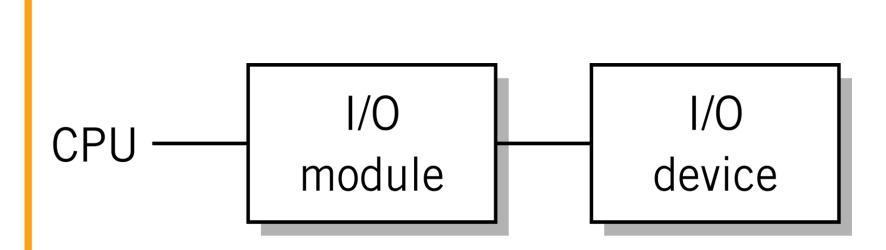

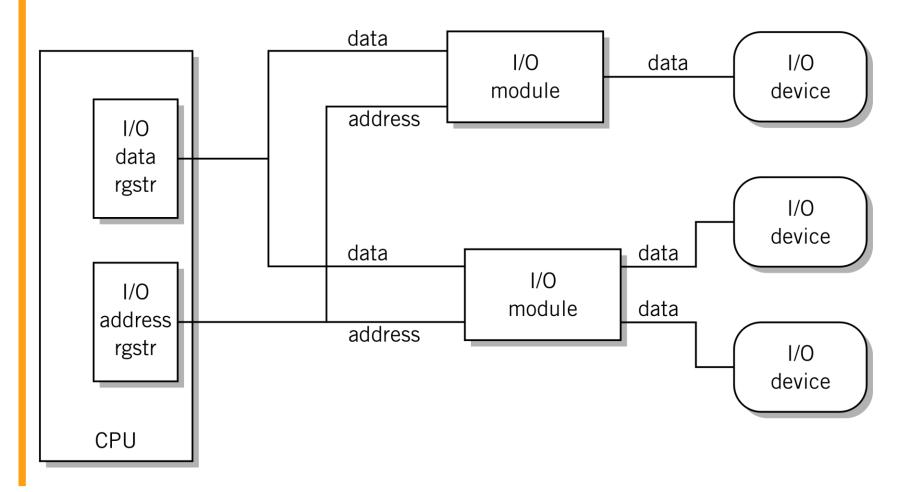

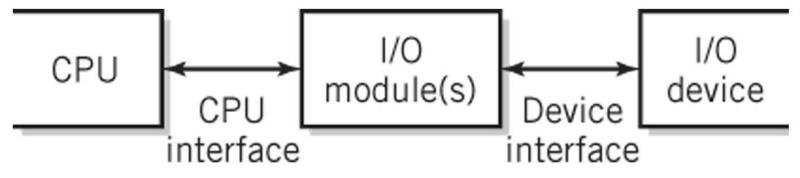

### Hardware Component

- Input/Output devices

- Storage Devices

- CPU Central Processing Unit

- ALU: arithmetic/logic unit

- CU: control unit

- Interface unit

- Memory

- Short-term storage for CPU calculations

### - Typical Personal Computer System

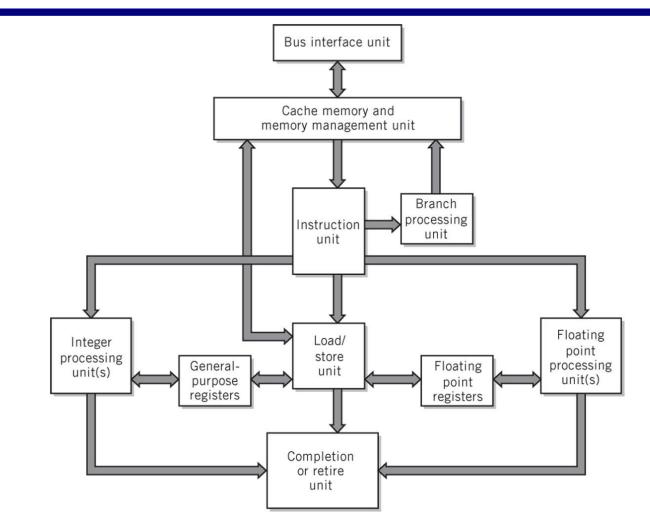

### **CPU: Central Processing Unit**

- ALU: arithmetic/logic unit

- Performs arithmetic and Boolean logical calculations

- CU: control unit

- Controls processing of instructions

- Controls movement of data within the CPU

- Interface unit

- Moves instructions and data between the CPU and other hardware components

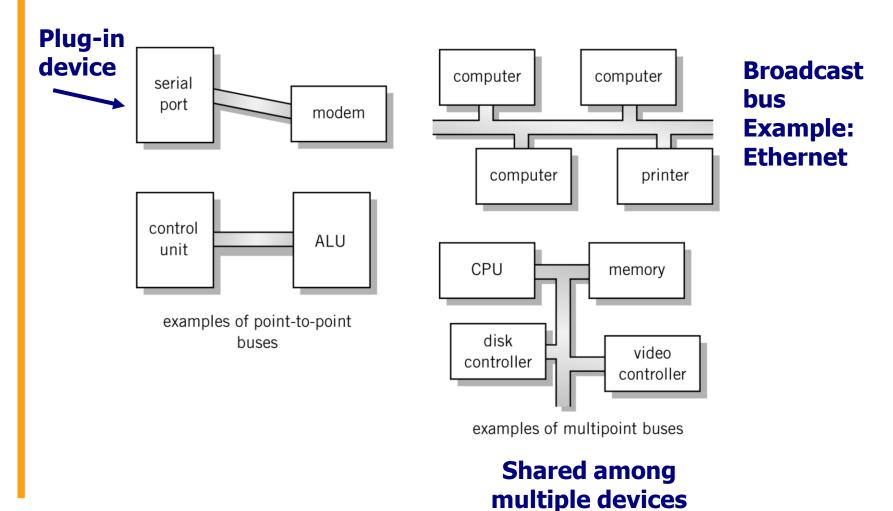

- Bus: bundle of wires that carry signals and power between different components

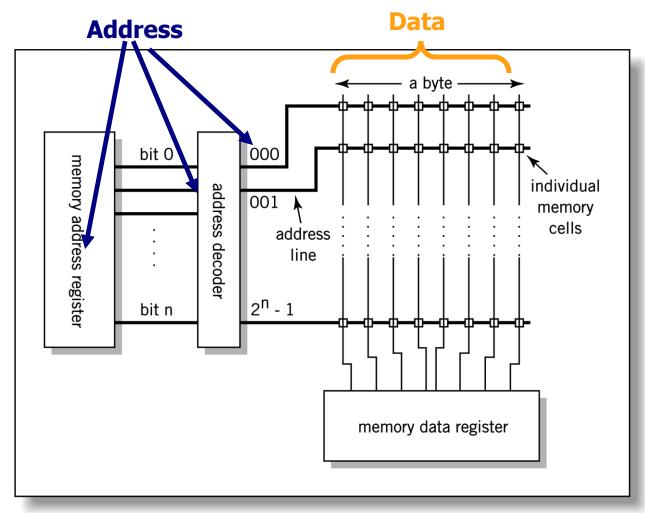

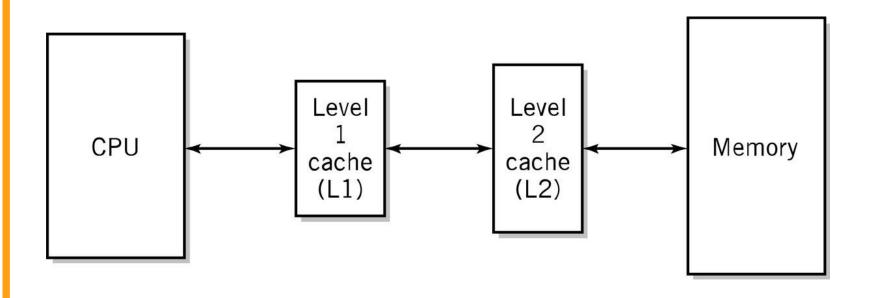

### Memory

- Also known as primary storage, working storage, working storage, and RAM (random access memory)

- Consists of bits, each of which hold a value of either 0 or 1 (8 bits = 1 byte)

- Holds both instructions and data of a computer program (stored program concept)

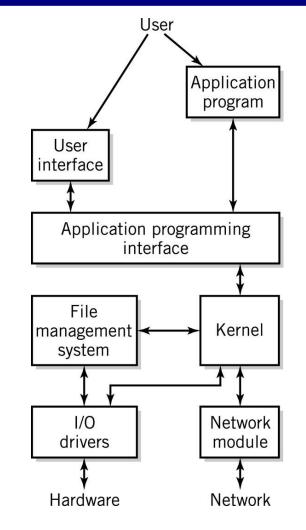

### Software Component

- Applications

- Operating System

- API: application program interface

- File management

- I/O

- Kernel

- Memory management

- Resource scheduling

- Program communication

- Security

- Network Module

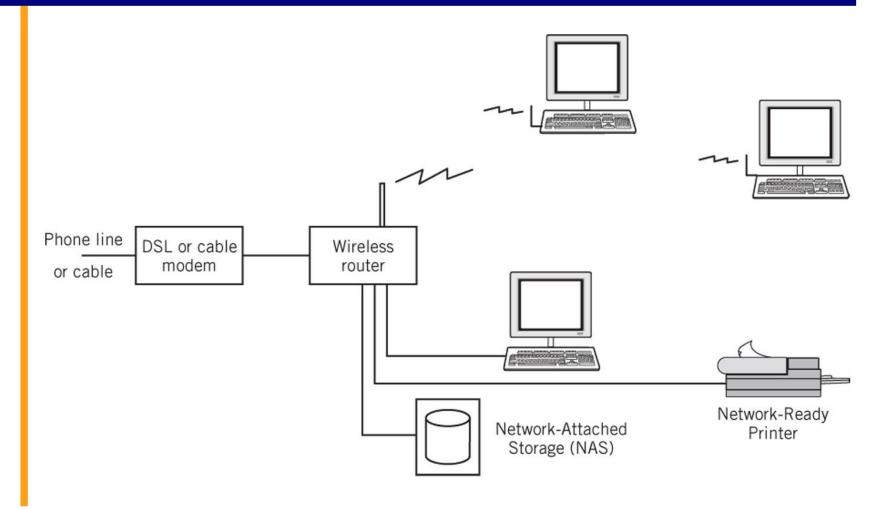

### **Communications** Component

#### Hardware

- Communication channels

- Physical connections between computer systems

- Examples: wire cable, phone lines, fiber optic cable, infrared light, radio waves

- Interface hardware

- Handles communication between the computer and the communication channel

- Modem or network interface card (NIC)

#### Software

- Establish connections

- Control flow of data

- Directs data to the proper applications for use

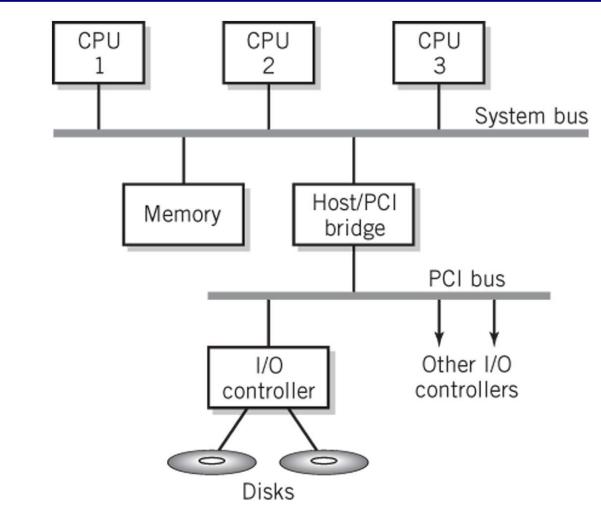

### **Computer Systems**

All computer systems, no matter how complex, consists of the following:

- At least one CPU

- Memory to hold programs and data

- I/O devices

- Long-term storage

### **Computer Systems Examples**

IBM System z10 EC Mainframe

HP Laptop Computer

### Virtualization

- Virtual (American Heritage Dictionary)

- Existing or result in essence or effect though not in actual fact, form or name

- Created, simulated, or carried on by means of a computer or computer network

- Computer systems examples

- Virtual memory

- Virtual networks

- Java Virtual Machine

### Protocols

- Common ground rules of communication between computers, I/O devices, and many software programs

- Examples

- HTTP: between Web servers and Web browsers

- TCP/IP: between computers on the Internet and local area networks

- SATA: between storage devices and computers

- XML,RSS, SIP: new protocols

### **Standards**

- Created to ensure universal compatibility of data formats and protocols

- May be created by committee or may become a de facto standard through popular use

- Examples:

- Computer languages: Java, SQL, C, JavaScript

- Display standards: Postscript, MPEG-2, JPEG, GIF

- Character set standards: ASCII, Unicode, EBCDIC

- Multimedia standards: MPEG-2, MPEG-4, DivX, MP3

### **Textbook Overview**

- Web site: <u>http://www.wiley.com/college/englander</u>

- Part 1 (Chapters 1-2)

- Overview of computer systems

- Part 2 (Chapters 3-5)

- Number systems and data formats

- Part 3 (Chapters 6-11)

- Computer architecture and hardware operation

- Part 4 (Chapters 12-14)

- Networks and data communications

- Part 5 (Chapters 15-18)

- Software component operating systems

- Part 6 (Supplementary Chapters S1-S4)

- Digital logic, systems examples, instruction addressing modes, programming tools

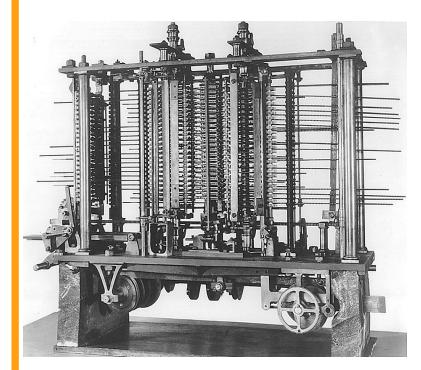

### **Early History**

- 1642: Blaise Pascal invents a calculating machine

- 1801: Joseph Marie Jacquard invents a loom that uses punch cards

- 1800's:

- Charles Babbage attempts to build an analytical engine (mechanical computer)

- Augusta Ada Byron develops many of the fundamental concepts of programming

- George Boole invents Boolean logic.

### **Modern Computer Development**

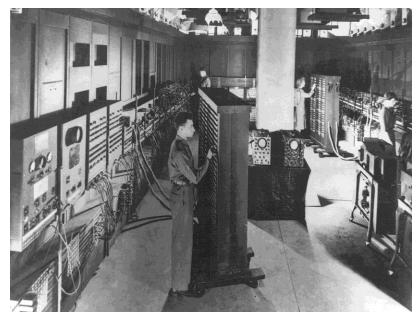

- 1937: Mark I is built (Aiken, Harvard University, IBM).

- First electronic computer using relays.

- 1939: ABC is built

- First fully electronic digital computer. Used vacuum tubes.

- 1943-46: ENIAC (Mauchly, Eckert, University of Pennsylvania).

- First general purpose digital computer.

- 1945: Von Neumann architecture proposed.

- Still the standard for present day computers.

- 1947: Creation of transistor

- (Bardeen, Shockley, Brattain, Bell Labs).

- 1951-2: EDVAC and IAS

### **Early Computers**

#### Babbage's Analytical Engine

ENIAC

## **System Software History**

- Early computers had no operating systems and were single user systems

- Programs were entered using switches for each bit or by plugging wires into a panel

- 1953-54: First operating system was built by General Motors Research Laboratories for their IBM 701 computer

- Other early systems

- FORTRAN Monitor System (FMS)

- IBSYS

- Share Operating System (SOS)

### **Operating System Development**

- 1963: Master Control Program (MCP) by Burroughs. Included many modern OS features.

- 1964: OS/360 by IBM. Included batch processing of programs.

- 1962: MIT Project MAC created a time-sharing OS called CTSS. Shortly afterwards, MIT, Bell Labs, and GE developed Multics (Multiplexed Information and Computing Services).

- After Bell Labs withdrew from the Multics project, Ken Thompson developed a personal operating system called UNIX using assembly language.

- Dennis Ritchie developed the programming language C which was used to rewrite much of UNIX in a highlevel language.

- UNIX introduced

- A hierarchical file system

- The shell concept

- Document production and formatting

- Tools for networked and distributed processing

### **Graphical User Interfaces**

- 1960s: Doug Englebart (Stanford Research Institute)

- Invented windows and a mouse interface

- 1970s: Xerox PARC

- Creates a practical windowing system for the Dynabook project

- 1980s: Steve Jobs (Apple)

- Developed the Apple Lisa and MacIntosh

### **IBM PC**

- 1982: Stand-alone, single user computer

- PC-DOS, MS-DOS (disk operating system)

- Later versions of DOS added

- Hierarchical directory file storage

- File redirection

- Better memory management

- Windowing systems

- Windows 2.0, Windows 3.1, Windows 95

- Windows NT, Windows XP, Windows Vista

- Windows 7

### Communications

- 1960s and 1970s: users communicated on multiterminal computer systems using talk and email facilities

- 1971: Ray Tomlinson creates the standard username@hostname email standard

- Modems permitted users to login to office systems, electronic bulletin board systems, Compuserve, AOL, and Prodigy

- 1969: ARPANET begun

- 1985: First TCP-IP wide area network

- 1991: Tim Berners Lee develops the concepts that become the World Wide Web

- 1993: Max Andreessen develops Mosaic, the first graphical browser

### Copyright 2010 John Wiley & Sons

All rights reserved. Reproduction or translation of this work beyond that permitted in section 117 of the 1976 United States Copyright Act without express permission of the copyright owner is unlawful. Request for further information should be addressed to the Permissions Department, John Wiley & Sons, Inc. The purchaser may make back-up copies for his/her own use only and not for distribution or resale. The Publisher assumes no responsibility for errors, omissions, or damages caused by the use of these programs or from the use of the information contained herein."

### CHAPTER 2: Introduction to Systems Concepts and Systems Architecture

### The Architecture of Computer Hardware, Systems Software & Networking: An Information Technology Approach 4th Edition, Irv Englander John Wiley and Sons ©2010

PowerPoint slides authored by Wilson Wong, Bentley University PowerPoint slides for the 3<sup>rd</sup> edition were co-authored with Lynne Senne, Bentley University

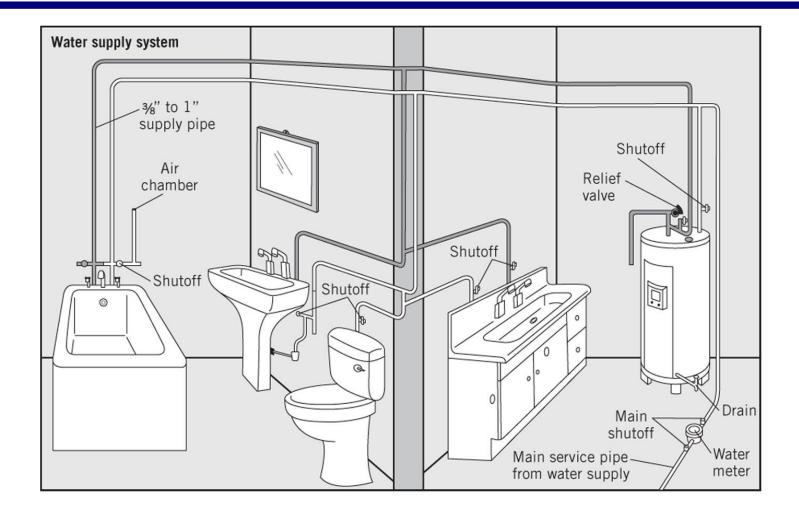

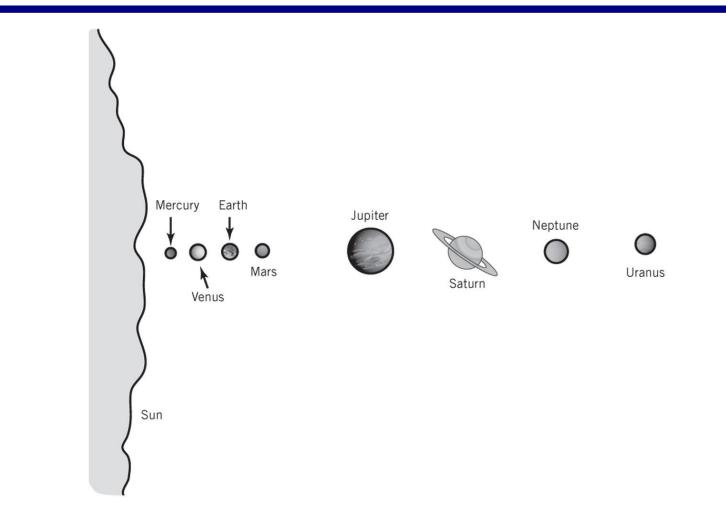

### What is a system?

- What do the following systems have in common?

- 1. Plumbing system

- 2. Solar system

- 3. Home network system

- 4. Inventory control system

## **Plumbing System**

# Solar System

# Home Network System

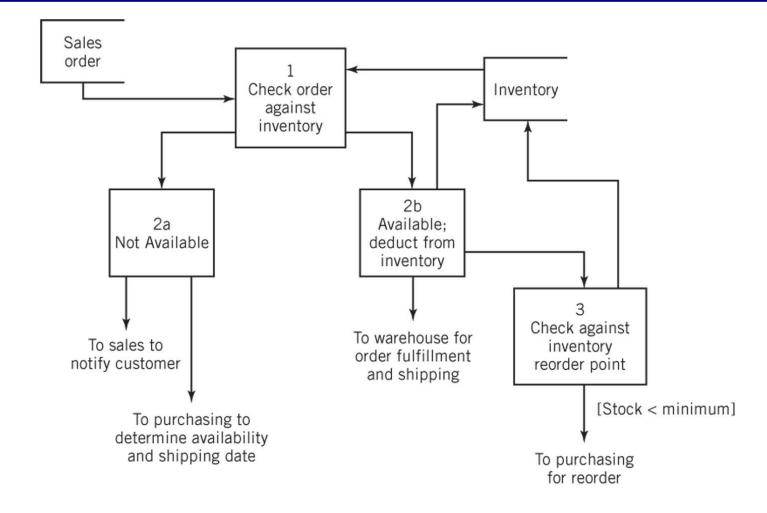

# **Inventory Control System**

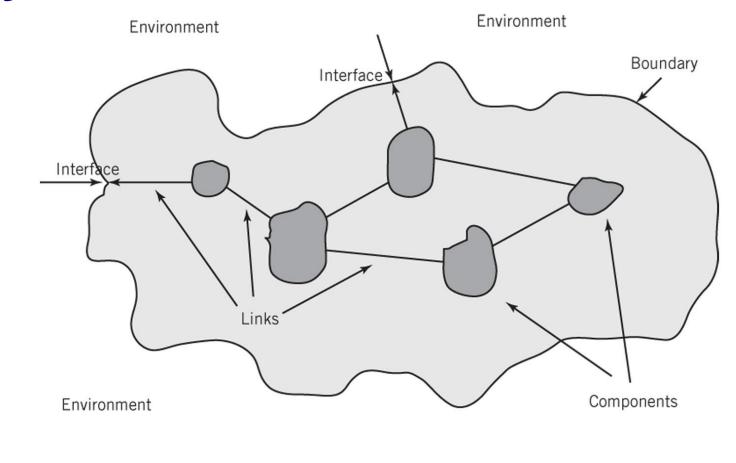

# **Definition of a System**

"A systems is a collection of components linked together and organized in such a way as to be recognizable as a single unit."

- Linked components of a system also define the boundary for the system

- The environment is anything outside of the system

# General Representation of a System

Environment

# **System Decomposition**

- Components

- May be irreducible or

- May be subsystems

- Decomposition

- The division of a system into its components and linkages

- Hierarchical

# **System Architecture**

"The fundamental properties, and the patterns of relationships, connections, constraints, and linkages among the components and between the system and its environment are known collectively as the architecture of the system"

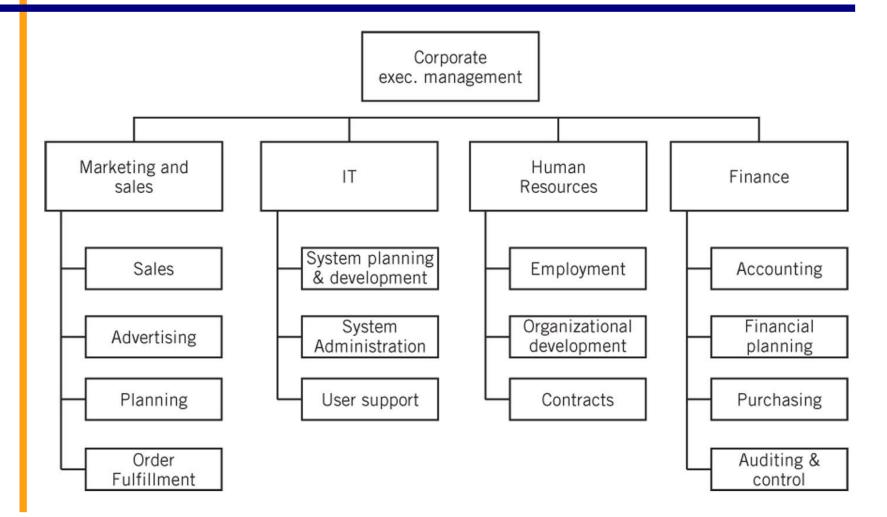

# **Abstractions of Systems**

- How are the following two abstractions of a business system different from one another?

- How are these abstractions different from the real business system?

# **Business Organization Chart**

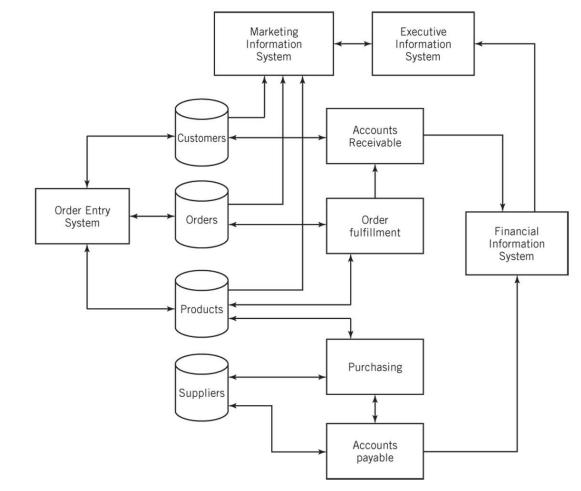

## Business Application Architecture

# **IT System Architectures**

- Distributed processing systems

- Client-Server Computing

- 2-tier architecture

- 3-tier architecture

- N-tier architecture

- Web-Based Computing

- Peer-to-Peer Computing

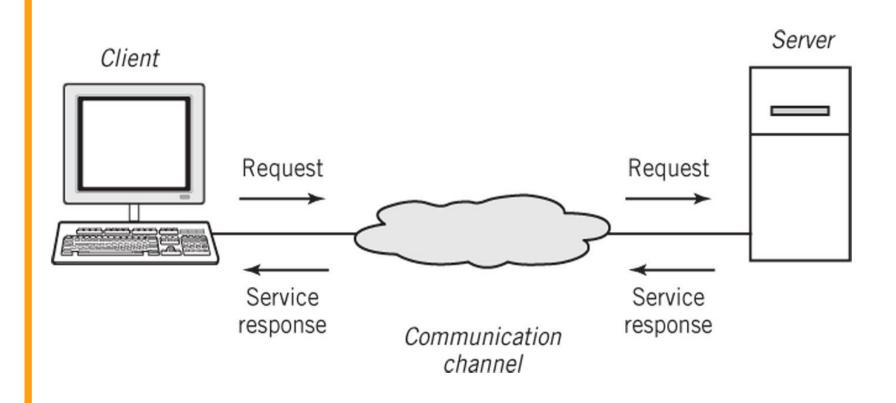

# **Client-Server Computing**

- A program on a client computer requests services from a program on a server computer

- Examples:

- Email services, file services, print services, directory services, Web services, database services, application services, remote access services

### Basic Client-Server Architecture

Copyright 2010 John Wiley & Sons, Inc.

### Advantages of Client-Server Architecture

- Centralization of services permits

- easier administration of services by IT professionals

- easier availability and location by users

- consistency of resources, such as files and data, can be managed and assured

- more efficient and cost-effective hardware procurement through purchasing a small number of very powerful computers

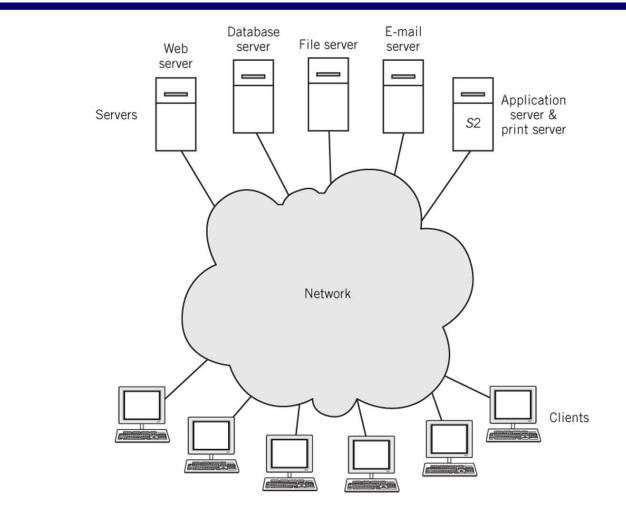

### **Clients and Servers on a Network**

Copyright 2010 John Wiley & Sons, Inc.

\*

# **Multi-tier Architectures**

- Two-tier architecture

- Two computers are involved in a service.

- Example: Web-browser and Web server model used in intranets and on the Internet

- Three-tier architecture

- Three computers are involved in a service

- Example: client computer, Web server, database server

- N-tier architecture

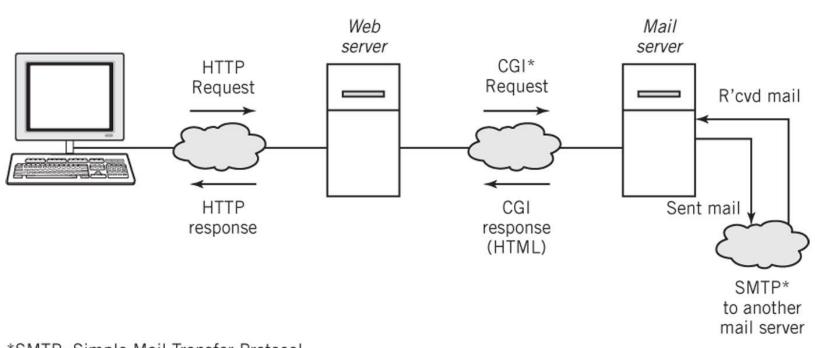

### **Three-tier Architecture**

\*SMTP: Simple Mail Transfer Protocol \*CGI: Common Gateway Interface

# **Peer-to-Peer Computing**

- Computers on a network are treated as equals

- Each computer can share resources with the other computers on the network

- Disadvantages

- Difficult to establish centralized control of services

- Difficult to locate services

- Difficult to synchronize versions of files or software

- Difficult to secure network from unauthorized access and from viruses

- Advantages

- Sharing files between personal computers

- Internet file sharing

# **Hybrid Model of Computing**

- Client-server technology used to locate systems and files

- Then systems can participate in peer-topeer transactions

- Examples

- Instant messaging

- Skype

- Napster

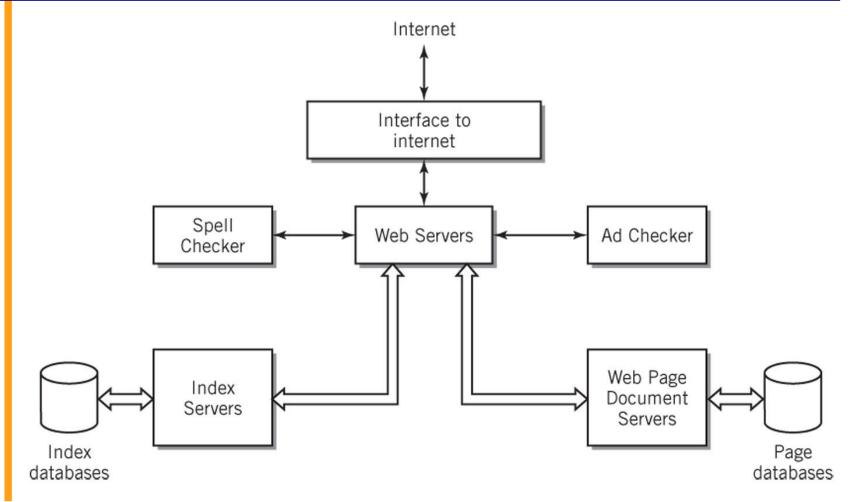

# **Google: System Architecture**

- Provide powerful, fast search capability for material on the Internet

- Derive income from advertising that is targeted to each user based on their searches

- Basic requirements

- Capable of responding to millions of simultaneous requests from all over the world

- Perform a web crawl of the Internet retrieve and organize data

- Establish ranking of results with appropriately targeted advertising

- High reliability of the system

- System is easily scalable and cost effective

#### Google Data Center Search Application Architecture

J.

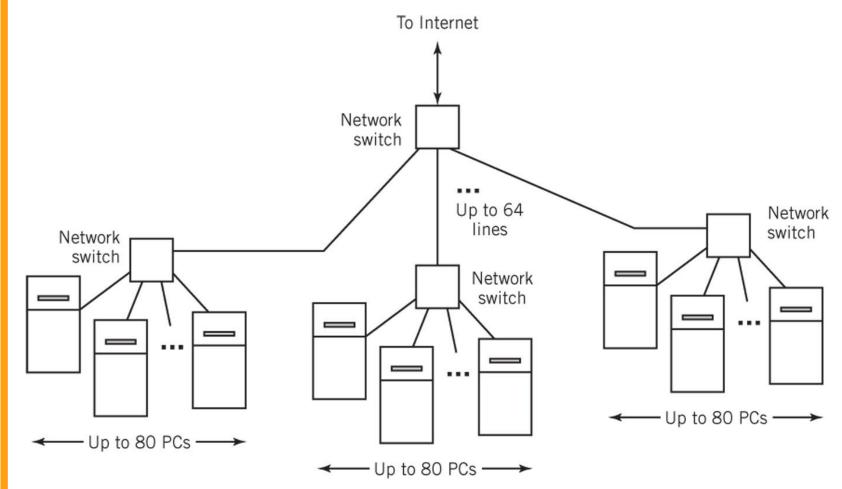

### Simplified Google System Hardware Architecture

Copyright 2010 John Wiley & Sons, Inc.

J.

#### Copyright 2010 John Wiley & Sons

All rights reserved. Reproduction or translation of this work beyond that permitted in section 117 of the 1976 United States Copyright Act without express permission of the copyright owner is unlawful. Request for further information should be addressed to the Permissions Department, John Wiley & Sons, Inc. The purchaser may make back-up copies for his/her own use only and not for distribution or resale. The Publisher assumes no responsibility for errors, omissions, or damages caused by the use of these programs or from the use of the information contained herein."

# CHAPTER 3: Number Systems

#### The Architecture of Computer Hardware and Systems Software & Networking: An Information Technology Approach 4th Edition, Irv Englander John Wiley and Sons ©2010

PowerPoint slides authored by Wilson Wong, Bentley University PowerPoint slides for the 3<sup>rd</sup> edition were co-authored with Lynne Senne, Bentley University

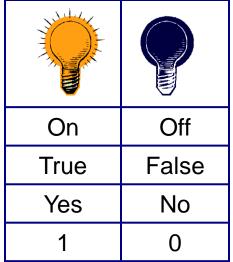

# Why Binary?

- Early computer design was decimal

- Mark I and ENIAC

- John von Neumann proposed binary data processing (1945)

- Simplified computer design

- Used for both instructions and data

- Natural relationship between on/off switches and calculation using Boolean logic

# **Counting and Arithmetic**

- Decimal or base 10 number system

- Origin: counting on the fingers

- "Digit" from the Latin word digitus meaning "finger"

- Base: the number of different digits including zero in the number system

- Example: Base 10 has 10 digits, 0 through 9

- Binary or base 2

- Bit (binary digit): 2 digits, 0 and 1

- Octal or base 8: 8 digits, 0 through 7

- Hexadecimal or base 16: 16 digits, 0 through F

Examples: 10<sub>10</sub> = A<sub>16</sub>; 11<sub>10</sub> = B<sub>16</sub>

# **Keeping Track of the Bits**

- Bits commonly stored and manipulated in groups

- 8 bits = 1 byte

- 4 bytes = 1 word (in many systems)

- Number of bits used in calculations

- Affects accuracy of results

- Limits size of numbers manipulated by the computer

#### **Numbers: Physical Representation**

- Different numerals, same number of oranges

- Cave dweller: IIIII

- Roman: V

- Arabic: 5

- Different bases, same number of oranges

- **5**10

- **1**01<sub>2</sub>

- 12<sub>3</sub>

# **Number System**

- Roman: position independent

- Modern: based on positional notation (place value)

- Decimal system: system of positional notation based on powers of 10.

- Binary system: system of positional notation based powers of 2

- Octal system: system of positional notation based on powers of 8

- Hexadecimal system: system of positional notation based powers of 16

# Positional Notation: Base 10

#### $527 = 5 \times 10^2 + 2 \times 10^1 + 7 \times 10^0$

| 100's pla | ice 10's        | olace           | 1's place       |  |

|-----------|-----------------|-----------------|-----------------|--|

|           |                 |                 |                 |  |

| Place     | 10 <sup>2</sup> | 10 <sup>1</sup> | 10 <sup>0</sup> |  |

| Value     | 100             | 10              | 1               |  |

| Evaluat   | 5 x 100         | 2 x 10          | 7 x1            |  |

| е         |                 |                 |                 |  |

| Sum       | 500             | 20              | 7               |  |

# **Positional Notation: Octal**

#### $624_8 = 404_{10}$

| 64's place         | 8's place        |                | 1's            | s pl |

|--------------------|------------------|----------------|----------------|------|

|                    |                  |                |                |      |

| Place              | <mark>8</mark> 2 | 8 <sup>1</sup> | 8 <sup>0</sup> |      |

| Value              | 64               | 8              | 1              |      |

| Evaluate           | 6 x 64           | 2 x 8          | 4 x 1          |      |

| Sum for<br>Base 10 | 384              | 16             | 4              |      |

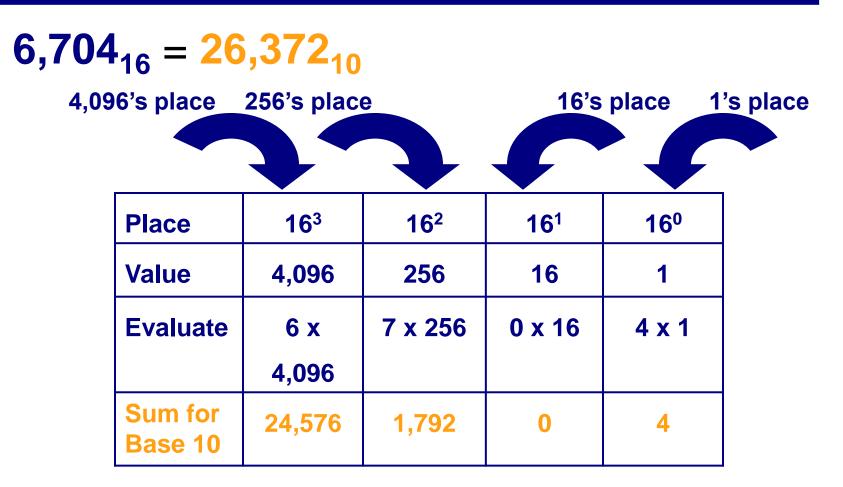

#### **Positional Notation: Hexadecimal**

# **Positional Notation: Binary**

#### **1101 0110**<sub>2</sub> = $214_{10}$

| Place              | 27      | <b>2</b> <sup>6</sup> | <b>2</b> <sup>5</sup> | 24    | <b>2</b> <sup>3</sup> | <b>2</b> <sup>2</sup> | 2 <sup>1</sup> | <b>2</b> <sup>0</sup> |

|--------------------|---------|-----------------------|-----------------------|-------|-----------------------|-----------------------|----------------|-----------------------|

| Value              | 128     | 64                    | 32                    | 16    | 8                     | 4                     | 2              | 1                     |

| Evaluate           | 1 x 128 | 1 x 64                | 0 x 32                | 1 x16 | 0 x 8                 | 1 x 4                 | 1 x 2          | 0 x 1                 |

| Sum for<br>Base 10 | 128     | 64                    | 0                     | 16    | 0                     | 4                     | 2              | 0                     |

# **Range of Possible Numbers**

- $R = B^{K}$  where

- R = range

- B = base

- K = number of digits

- Example #1: Base 10, 2 digits

- $R = 10^2 = 100$  different numbers (0...99)

- Example #2: Base 2, 16 digits

- $R = 2^{16} = 65,536 \text{ or } 64K$

- 16-bit PC can store 65,536 different number values

### **Decimal Range for Bit Widths**

| Bits | Digits | Range                          |

|------|--------|--------------------------------|

| 1    | 0+     | 2 (0 and 1)                    |

| 4    | 1+     | 16 (0 to 15)                   |

| 8    | 2+     | 256                            |

| 10   | 3      | 1,024 (1K)                     |

| 16   | 4+     | 65,536 (64K)                   |

| 20   | 6      | 1,048,576 (1M)                 |

| 32   | 9+     | 4,294,967,296 (4G)             |

| 64   | 19+    | Approx. 1.6 x 10 <sup>19</sup> |

| 128  | 38+    | Approx. 2.6 x 10 <sup>38</sup> |

#### **Base or Radix**

- Base:

- The number of different symbols required to represent any given number

- The *larger* the base, the *more* numerals are required

- Base 10: 0,1, 2,3,4,5,6,7,8,9

- Base 2: 0,1

- Base 8: 0,1,2, 3,4,5,6,7

- Base 16: 0,1,2,3,4,5,6,7,8,9,A,B,C,D,E,F

# Number of Symbols vs. Number of Digits

- For a given number, the *larger* the base

- the more symbols required

- but the *fewer* digits needed

- Example #1:

- **65**<sub>16</sub> **101**<sub>10</sub> **145**<sub>8</sub> **110 0101**<sub>2</sub>

- Example #2:

- $-11C_{16} 284_{10} 434_8 10001 1100_2$

# **Counting in Base 2**

| Binary |                       | Equivalent         |                    |                    |        |  |  |

|--------|-----------------------|--------------------|--------------------|--------------------|--------|--|--|

| Number | 8's (2 <sup>3</sup> ) | 4's (2²)           | 2's (21)           | 1's (2º)           | Number |  |  |

| 0      |                       |                    |                    | 0 x 2 <sup>0</sup> | 0      |  |  |

| 1      |                       |                    |                    | 1 x 2 <sup>0</sup> | 1      |  |  |

| 10     |                       |                    | 1 x 2 <sup>1</sup> | 0 x 2 <sup>0</sup> | 2      |  |  |

| 11     |                       |                    | 1 x 2 <sup>1</sup> | 1 x 2 <sup>0</sup> | 3      |  |  |

| 100    |                       | 1 x 2 <sup>2</sup> |                    |                    | 4      |  |  |

| 101    |                       | 1 x 2 <sup>2</sup> |                    | 1 x 2 <sup>0</sup> | 5      |  |  |

| 110    |                       | 1 x 2 <sup>2</sup> | 1 x 2 <sup>1</sup> |                    | 6      |  |  |

| 111    |                       | 1 x 2 <sup>2</sup> | 1 x 2 <sup>1</sup> | 1 x 2 <sup>0</sup> | 7      |  |  |

| 1000   | 1 x 2 <sup>3</sup>    |                    |                    |                    | 8      |  |  |

| 1001   | 1 x 2 <sup>3</sup>    |                    |                    | 1 x 2 <sup>0</sup> | 9      |  |  |

| 1010   | 1 x 2 <sup>3</sup>    |                    | 1 x 2 <sup>1</sup> |                    | 10     |  |  |

# **Base 10 Addition Table**

#### $3_{10} + 6_{10} = 9_{10}$

| + | 0 | 1 | 2 | 3 | 4        | 5 | 6  | 7  | 8  | 9  |

|---|---|---|---|---|----------|---|----|----|----|----|

| 0 | 0 | 1 | 2 | 3 | 4        | 5 | 6  | 7  | 8  | 9  |

| 1 | 1 | 2 | 3 | 4 | 5        | 6 | 7  | 8  | 9  | 10 |

| 2 | 2 | 3 | 4 | 5 | 6        | 7 | 8  | 9  | 10 | 11 |

| 3 | 3 | 4 | 5 | 6 | 7        | 8 | 9  | 10 | 11 | 12 |

| 4 | 4 | 5 | 6 | 7 | 8<br>etc | 9 | 10 | 11 | 12 | 13 |

# **Base 8 Addition Table**

| 3 <sub>8</sub> - | + 6 <sub>8</sub> | = 1 | 1 <sub>8</sub> |

|------------------|------------------|-----|----------------|

|                  |                  |     |                |

| • | • | • |    |    |    |    |    |    |    | -     |

|---|---|---|----|----|----|----|----|----|----|-------|

|   | + | 0 | 1  | 2  | 3  | 4  | 5  | 6  | 7  |       |

|   | 0 | 0 | 1  | 2  | 3  | 4  | 5  | 6  | 7  |       |

|   | 1 | 1 | 2  | 3  | 4  | 5  | 6  | 7  | 10 | (no 8 |

|   | 2 | 2 | 3  | 4  | 5  | 6  | 7  | 10 | 11 | of co |

|   | 3 | 3 | 4  | 5  | 6  | 7  | 10 | 11 | 12 |       |

|   | 4 | 4 | 5  | 6  | 7  | 10 | 11 | 12 | 13 |       |

|   | 5 | 5 | 6  | 7  | 10 | 11 | 12 | 13 | 14 |       |

|   | 6 | 6 | 7  | 10 | 11 | 12 | 13 | 14 | 15 |       |

|   | 7 | 7 | 10 | 11 | 12 | 13 | 14 | 15 | 16 |       |

|   |   |   |    |    |    |    |    |    |    |       |

(no 8 or 9, of course)

### **Base 10 Multiplication Table**

#### $3_{10} \times 6_{10} = 18_{10}$

| <br> | - |   | 10 |    |    |    |    |    |    |    |    |

|------|---|---|----|----|----|----|----|----|----|----|----|

| х    |   | 0 | 1  | 2  | 3  | 4  | 5  | 6  | 7  | 8  | 9  |

| 0    |   |   |    |    | 0  |    |    |    |    |    |    |

| 1    |   |   | 1  | 2  | 3  | 4  | 5  | 6  | 7  | 8  | 9  |

| 2    |   |   | 2  | 4  | 6  | 8  | 10 | 12 | 14 | 16 | 18 |

| 3    |   |   | 3  | 6  | 9  | 12 | 15 | 18 | 21 | 24 | 27 |

| 4    |   | 0 | 4  | 8  | 12 | 16 | 20 | 24 | 28 | 32 | 36 |

| 5    |   |   | 5  | 10 | 15 | 20 | 25 | 30 | 35 | 40 | 45 |

| 6    |   |   | 6  | 12 | 18 | 24 | 30 | 36 | 42 | 48 | 54 |

| 7    |   |   | 7  | 14 | 21 | 28 | 35 | 42 | 49 | 56 | 63 |

|      |   |   |    |    |    |    |    |    |    |    |    |

Copyright 2010 John Wiley & Sons, Inc.

etc.

### **Base 8 Multiplication Table**

#### $3_8 \times 6_8 = 22_8$ Х

Copyright 2010 John Wiley & Sons, Inc.

J.

### Addition

| Base        | Problem        | Largest Single Digit |

|-------------|----------------|----------------------|

| Decimal     | 6<br><u>+3</u> | 9                    |

| Octal       | 6<br><u>+1</u> | 7                    |

| Hexadecimal | 6<br><u>+9</u> | F                    |

| Binary      | 1<br><u>+0</u> | 1                    |

### Addition

| Base        | Problem        | Carry        | Answer |

|-------------|----------------|--------------|--------|

| Decimal     | 6<br><u>+4</u> | Carry the 10 | 10     |

| Octal       | 6<br><u>+2</u> | Carry the 8  | 10     |

| Hexadecimal | 6<br><u>+A</u> | Carry the 16 | 10     |

| Binary      | 1<br><u>+1</u> | Carry the 2  | 10     |

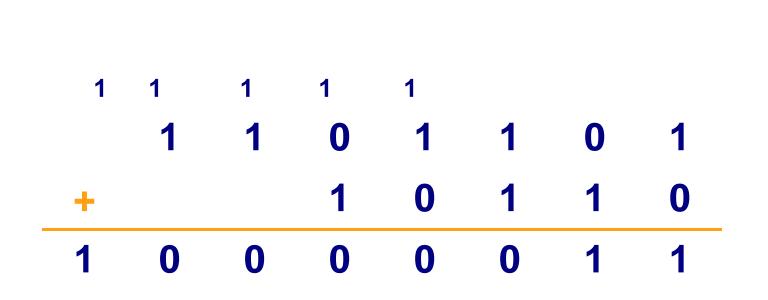

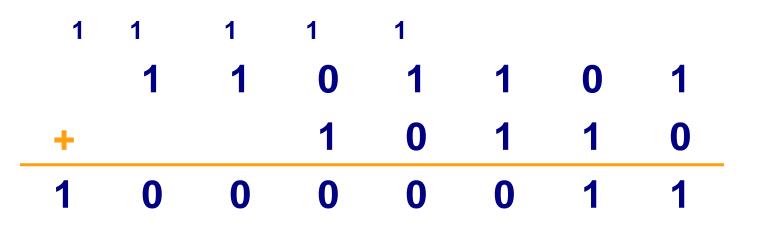

## **Binary Arithmetic**

# **Binary Arithmetic**

- Addition

- Boolean using XOR and AND

- Multiplication

- AND

- Shift

- Division

| + |        | 0 | 1   |

|---|--------|---|-----|

|   | 0<br>1 | 0 | 1   |

|   | 1      | 1 | 10  |

|   |        |   |     |

|   |        | 0 | 1   |

| Χ |        | U | I I |

| X | 0      | 0 | 0   |

| X | 0<br>1 |   | -   |

#### **Binary Arithmetic: Boolean Logic**

- Boolean logic without performing arithmetic

- EXCLUSIVE-OR

- Output is "1" only if either input, but *not* both inputs, is a "1"

- AND (carry bit)

- Output is "1" if and only both inputs are a "1"

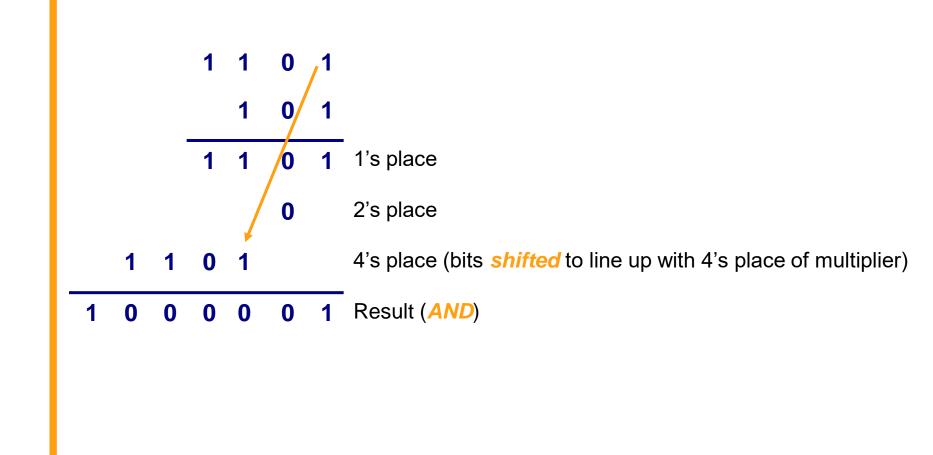

# **Binary Multiplication**

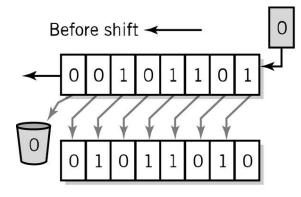

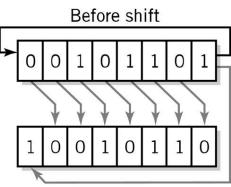

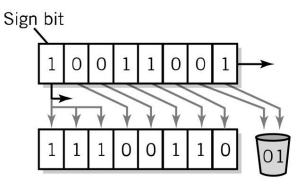

- Boolean logic without performing arithmetic

- AND (carry bit)

- Output is "1" if and only both inputs are a "1"

- Shift

- Shifting a number in any base left one digit multiplies its value by the base

- Shifting a number in any base right one digit divides its value by the base

- Examples:

□ 10<sub>10</sub> shift *left* = 100<sub>10</sub>

□ 10<sub>10</sub> shift *right* = 1<sub>10</sub>

**10**<sub>2</sub> shift *left* =  $100_2$  **10**<sub>2</sub> shift *right* =  $1_2$

# **Binary Multiplication**

# **Converting from Base 10**

#### Powers Table

| Power<br>Base | 8   | 7   | 6  | 5      | 4      | 3     | 2   | 1  | 0 |

|---------------|-----|-----|----|--------|--------|-------|-----|----|---|

| 2             | 256 | 128 | 64 | 32     | 16     | 8     | 4   | 2  | 1 |

| 8             |     |     |    | 32,768 | 4,096  | 512   | 64  | 8  | 1 |

| 16            |     |     |    |        | 65,536 | 4,096 | 256 | 16 | 1 |

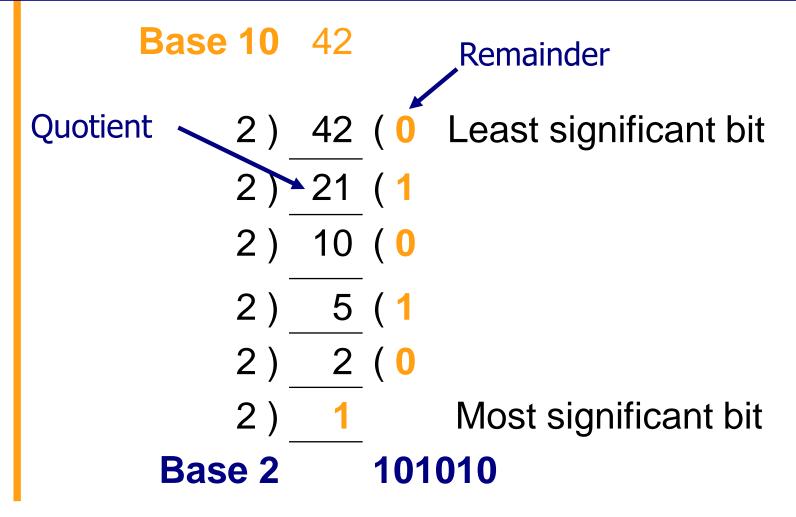

#### $42_{10} = 101010_2$

| Power<br>Base | 6  | 5            | 4            | 3           | 2          | 1          | 0           |

|---------------|----|--------------|--------------|-------------|------------|------------|-------------|

| 2             | 64 | 32           | 16           | 8           | 4          | 2          | 1           |

|               |    | 1            | 0            | 1           | 0          | 1          | 0           |

| Integer       |    | 42/32<br>= 1 | 10/16<br>= 0 | 10/8<br>= 1 | 2/4<br>= 0 | 2/2<br>= 1 | ,0/1<br>= 0 |

| Remainder     |    | 10           | 10           | 2           | 2          | 0          | 0           |

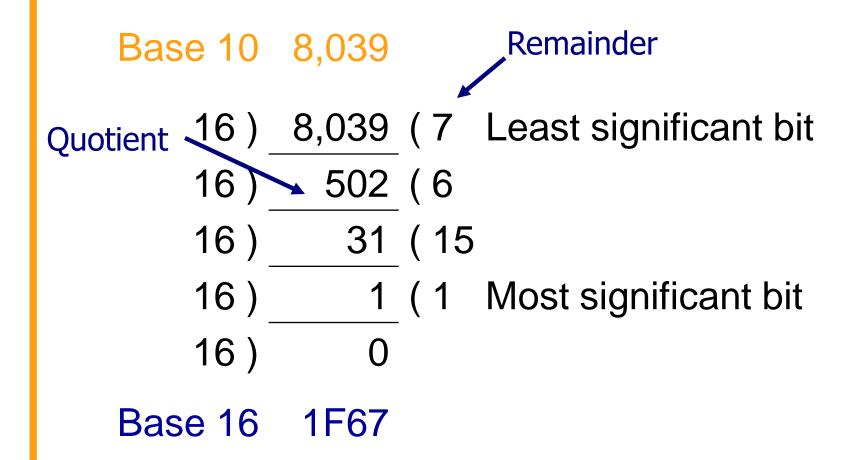

#### **5**,**735**<sub>10</sub> = **1667**<sub>16</sub>

| Power<br>Base | 4      | 3                        | 2                     | 1               | 0 |

|---------------|--------|--------------------------|-----------------------|-----------------|---|

| 16            | 65,536 | 4,096                    | 256                   | 16              | 1 |

|               |        | 1                        | 6                     | 6               | 7 |

| Integer       |        | 5,735 /4,096<br>= 1      | 1,639 / 256<br>= 6    | 103 /16<br>= 6  | 7 |

| Remainder     |        | 5,735 - 4,096<br>= 1,639 | 1,639 –1,536<br>= 103 | 103 – 96<br>= 7 |   |

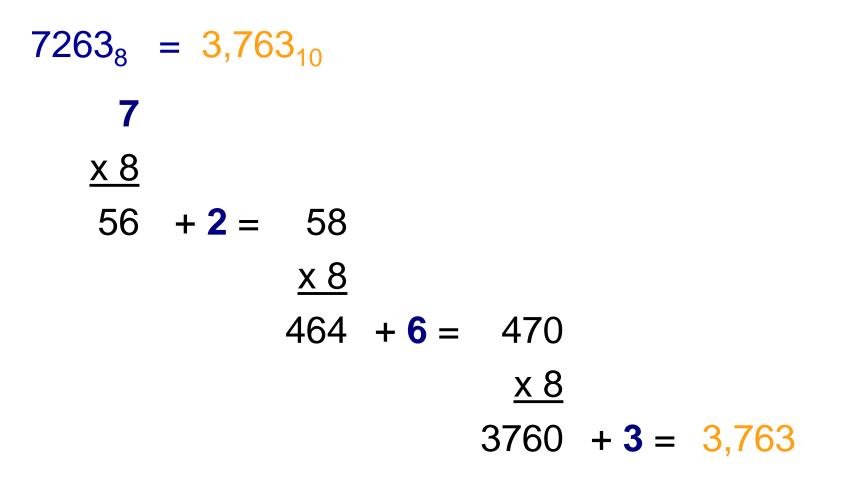

| 7263 <sub>8</sub> | = | 3,763 <sub>10</sub> |

|-------------------|---|---------------------|

|-------------------|---|---------------------|

| Power              | 8 <sup>3</sup> | <mark>8</mark> 2 | 8 <sup>1</sup> | 8 <sup>0</sup> |

|--------------------|----------------|------------------|----------------|----------------|

|                    | 512            | 64               | 8              | 1              |

|                    | x 7            | x 2              | x 6            | x 3            |

| Sum for<br>Base 10 | 3,584          | 128              | 48             | 3              |

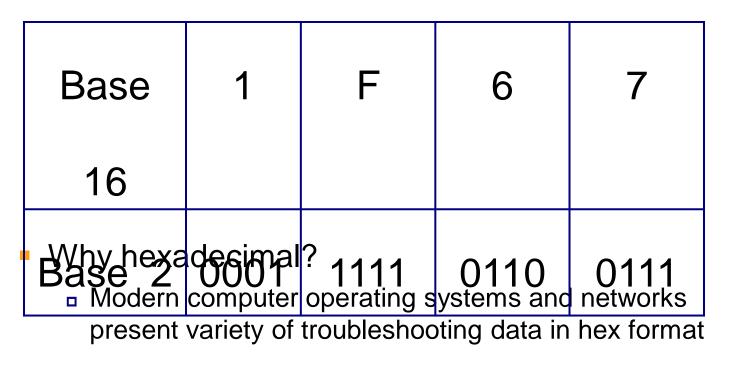

- The nibble approach

- Hex easier to read and write than binary

#### Fractions

- Number point or radix point

- Decimal point in base 10

- Binary point in base 2

- No exact relationship between fractional numbers in different number bases

- Exact conversion may be impossible

### **Decimal Fractions**

- Move the number point one place to the right

- Effect: multiplies the number by the base number

- Example: 139.0<sub>10</sub> = 1390<sub>10</sub>

- Move the number point one place to the left

- Effect: divides the number by the base number

- Example:  $139.0_{10} \longrightarrow 13.9_{10}$

# Fractions: Base 10 and Base 2

#### **.2589**<sub>10</sub>

| Place    | <b>10</b> -1 | 10 <sup>-2</sup> | 10 <sup>-3</sup> | 10-4      |

|----------|--------------|------------------|------------------|-----------|

| Value    | 1/10         | 1/100            | 1/1000           | 1/10000   |

| Evaluate | 2 x 1/10     | 5 x 1/100        | 8 x 1/1000       | 9 x1/1000 |

| Sum      | .2           | .05              | .008             | .0009     |

#### $.101011_2 = 0.671875_{10}$

| Place    | <b>2</b> -1 | <b>2</b> -2 | <b>2</b> <sup>-3</sup> | 2-4      | <b>2</b> <sup>-5</sup> | <b>2</b> <sup>-6</sup> |

|----------|-------------|-------------|------------------------|----------|------------------------|------------------------|

| Value    | 1/2         | 1/4         | 1/8                    | 1/16     | 1/32                   | 1/64                   |

| Evaluate | 1 x 1/2     | 0 x 1/4     | 1x 1/8                 | 0 x 1/16 | 1 x 1/32               | 1 x 1/64               |

| Sum      | .5          |             | 0.125                  |          | 0.03125                | 0.015625               |

#### Fractions: Base 10 and Base 2

- No general relationship between fractions of types 1/10<sup>k</sup> and 1/2<sup>k</sup>

- Therefore a number representable in base 10 may not be representable in base 2

- But: the converse is true: all fractions of the form 1/2<sup>k</sup> can be represented in base 10

- Fractional conversions from one base to another are stopped

- If there is a rational solution or

- When the desired accuracy is attained

# **Mixed Number Conversion**

- Integer and fraction parts must be converted separately

- Radix point: fixed reference for the conversion

- Digit to the left is a unit digit in every base

- B<sup>0</sup> is always 1 regardless of the base

#### Copyright 2010 John Wiley & Sons

All rights reserved. Reproduction or translation of this work beyond that permitted in section 117 of the 1976 United States Copyright Act without express permission of the copyright owner is unlawful. Request for further information should be addressed to the Permissions Department, John Wiley & Sons, Inc. The purchaser may make back-up copies for his/her own use only and not for distribution or resale. The Publisher assumes no responsibility for errors, omissions, or damages caused by the use of these programs or from the use of the information contained herein."

### CHAPTER 4: Data Formats

#### The Architecture of Computer Hardware, Systems Software & Networking: An Information Technology Approach 4th Edition, Irv Englander John Wiley and Sons ©2010

PowerPoint slides authored by Wilson Wong, Bentley University PowerPoint slides for the 3<sup>rd</sup> edition were co-authored with Lynne Senne, Bentley University

#### **Data Formats**

- Computers

- Process and store all forms of data in binary format

- Human communication

- Includes language, images and sounds

- Data formats:

- Specifications for converting data into computerusable form

- Define the different ways human data may be represented, stored and processed by a computer

#### **Sources of Data**

- Binary input

- Begins as discrete input

- Example: keyboard input such as A 1+2=3 math

- Keyboard generates a binary number code for each key

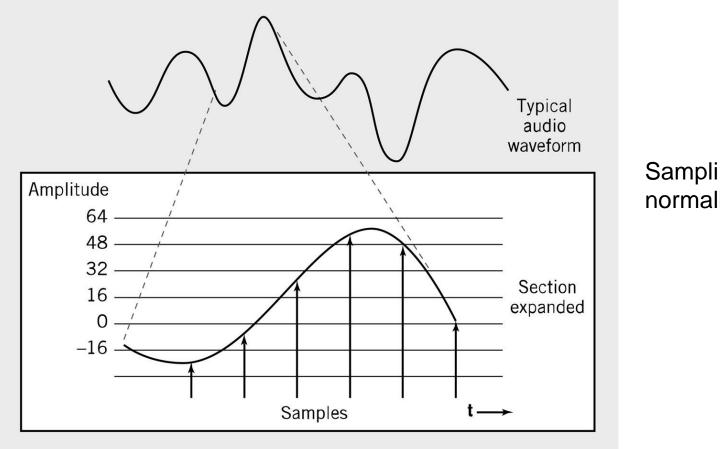

- Analog

- Continuous data such as sound or images

- Requires hardware to convert data into binary numbers

Figure 3.1 with this color scheme

#### **Common Data Representations**

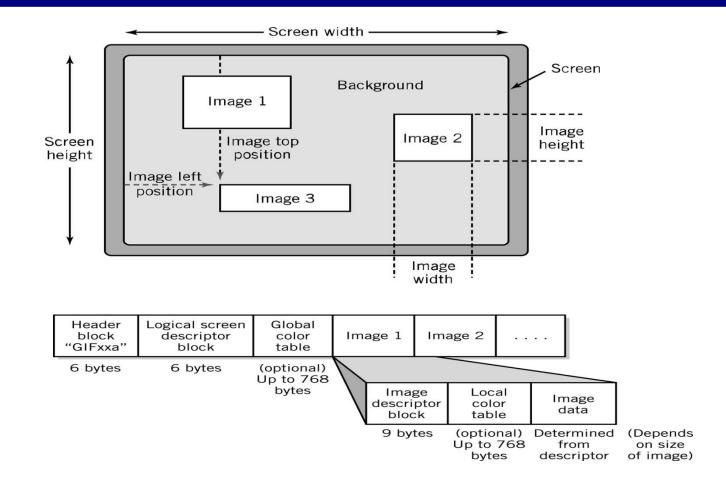

| Type of Data               | Standard(s)                                                                                                                       |

|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------|

| Alphanumeric               | Unicode, ASCII, EDCDIC                                                                                                            |

| Image (bitmapped)          | <ul> <li>GIF (graphical image format)</li> <li>TIF (tagged image file format)</li> <li>PNG (portable network graphics)</li> </ul> |

| Image (object)             | PostScript, JPEG, SWF (Macromedia Flash), SVG                                                                                     |

| Outline graphics and fonts | PostScript, TrueType                                                                                                              |

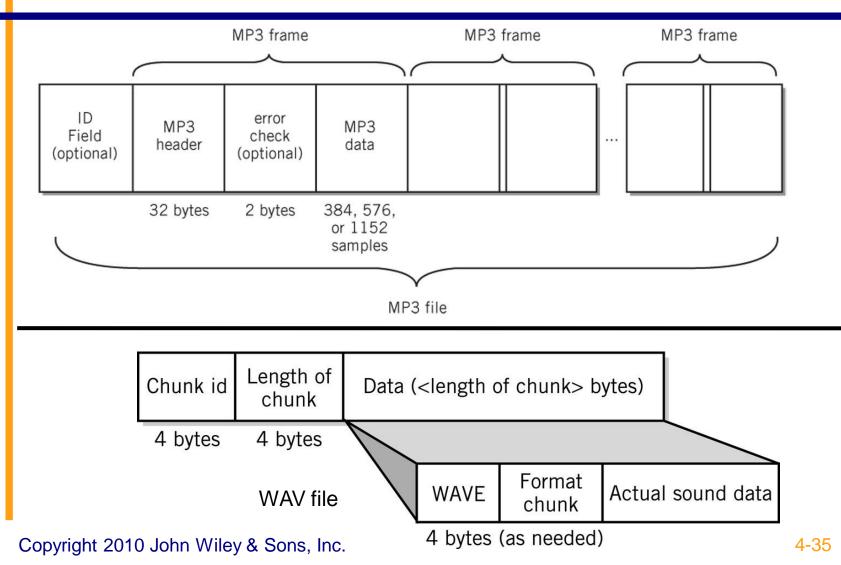

| Sound                      | WAV, AVI, MP3, MIDI, WMA                                                                                                          |

| Page description           | PDF (Adobe Portable Document<br>Format), HTML, XML                                                                                |

| Video                      | Quicktime, MPEG-2, RealVideo, WMV                                                                                                 |

### **Internal Data Representation**

- Reflects the

- Complexity of input source

- Type of processing required

- Trade-offs

- Accuracy and resolution

- Simple photo vs. painting in an art book

- Compactness (storage and transmission)

- More data required for improved accuracy and resolution

- Compression represents data in a more compact form

- *Metadata:* data that describes or interprets the meaning of data

- Ease of manipulation:

- Processing simple audio vs. high-fidelity sound

- Standardization

- Proprietary formats for storing and processing data (WordPerfect vs. Word)

- De facto standards: proprietary standards based on general user acceptance (PostScript)

# **Data Types: Numeric**